#### SINGLE-TRACK ASYNCHRONOUS PIPELINE TEMPLATE

by

Marcos Ferretti

A Dissertation Presented to the FACULTY OF THE GRADUATE SCHOOL UNIVERSITY OF SOUTHERN CALIFORNIA In Partial Fulfillment of the Requirements for the Degree DOCTOR OF PHILOSOPHY (ELECTRICAL ENGINEERING)

August 2004

Copyright 2004

Marcos Ferretti

# DEDICATION

To my wife.

#### ACKNOWLEDGMENTS

This work would not be possible without the vision and knowledge of my advisor, Peter A. Beerel. His support and guidance were essential for the development of new ideas. Also, he and his wife, Janet, were always available for help, creating a friendly and productive environment.

I would like to thank my friends, from the USC Asynchronous CAD/VLSI Group, for all these years of invaluable suggestions, comments and friendship: Sunan Tugsinavisut, Recep O. Ozdag, Hoshik Kim, Sangyun Kim, Jay Moon, Shantanu Awasthi and Pankaj Golani.

I am especially grateful to the USC professors, in particular, Massoud Pedram, Won Namgoong, Roger Zimmermann and Kian Kaviani, and to the USC Electrical Engineering staff, Tim Boston, Diane Demetras, Lisa I. Connell and Marylee Reynolds, for their patience and crucial help. Also, I am grateful to all my UNICAMP professors, including my former MS advisor, José Antonio Siqueira Dias, for all their efforts to teach me the foundations of electrical engineering and their support for my continuing studies at USC.

I would like to acknowledge the generous support from National Science Foundation Grant CCR-0086036 and the gifts from TRW, Fulcrum Microsystems and the MOSIS Educational Program.

Thanks are due to Helen Thompson, Sam Reynolds, Wes Hansford, and all the MOSIS support people for the great cooperation and effort to meet our needs.

I also would like to thank Andrew Lines for his encouraging comments and discussions, Mike Moacanin and Jeremy Boulton for helping with the temperature measurements.

It is important to acknowledge Prof. Rogerio C. Leite, Sergio C. Leite, Ichiro Aoki, Ricardo R. Maciel and Newton E. Fujii, whom I had the opportunity to work with. They contributed to shape my views of business, politics and friendship. They also encouraged me to pursue new knowledge and goals.

My deepest gratitude is reserved to my wife, Lilione, whose love, confidence and understanding never failed to me. I could never have done this work without her.

Lastly, I would like to thank my parents, Raul and Aurora, and my siblings, Nair, Santo e Geraldo, for supporting me throughout my life and for being there when I needed them.

## Contents

| Dedicationii |                       |        |                                          |   |  |  |  |  |

|--------------|-----------------------|--------|------------------------------------------|---|--|--|--|--|

| A            | Acknowledgmentsiii    |        |                                          |   |  |  |  |  |

| L            | List of Figures viii  |        |                                          |   |  |  |  |  |

| L            | List of Tablesxi      |        |                                          |   |  |  |  |  |

| L            | ist of                | f Tab  | lesxi                                    | i |  |  |  |  |

| A            | bstra                 | act    | xii                                      | i |  |  |  |  |

| 1            | Ι                     | ntroc  | luction1                                 | L |  |  |  |  |

|              | 1.1                   | Asyn   | chronous Design                          | ? |  |  |  |  |

|              | 1.2                   | Test   | structures5                              | ī |  |  |  |  |

|              | 1.3                   | Desi   | gn flow                                  | 5 |  |  |  |  |

|              | 1.4                   | Con    | tribution of this work                   | } |  |  |  |  |

|              | 1.5                   | Org    | anization                                | } |  |  |  |  |

| 2            | E                     | Backg  | ground10                                 | ) |  |  |  |  |

|              | 2.1                   | Asyn   | chronous channels                        | ) |  |  |  |  |

|              | 2.2                   | QDI    | weak-condition half-buffer (WCHB)12      | , |  |  |  |  |

|              | 2.3 GasP bundled data |        | P bundled data14                         | 1 |  |  |  |  |

|              | 2.4                   | Fine   | -grain vs. two dimensional pipelining15  | , |  |  |  |  |

| 3            | S                     | lingle | -Track Full-Buffer circuits17            | , |  |  |  |  |

|              | 3.1                   | STF    | B buffers                                | 7 |  |  |  |  |

|              | 3.2                   | STF    | B forks and joins22                      | , |  |  |  |  |

|              | 3.                    | 2.1    | Dual-rail STFB semi-weak-conditioned AND | ì |  |  |  |  |

|              | 3.                    | 2.2    | Dual-rail STFB non weak-conditioned AND  |   |  |  |  |  |

|              | 3.                    | 2.3    | Dual-rail STFB OR and STFB XORs          | ) |  |  |  |  |

|              | 3.                    | 2.4    | Dual-rail STFB non-conditional merge     |   |  |  |  |  |

|              |                       |        | V                                        | 1 |  |  |  |  |

|   | 4.10       | Timing margin: The ten transitions STFB template |    |

|---|------------|--------------------------------------------------|----|

|   |            | Static single-track protocol                     |    |

|   | 4.8        | Noise margin                                     |    |

|   | 4.7        | Reset tree                                       |    |

|   | 4.6        | Direct-path current analysis                     |    |

|   | 4.5        | Input channel reset transistors                  |    |

|   |            | The RCD sizing                                   |    |

|   | 4.5<br>4.4 | Output sub-cell STFB_POUT                        |    |

|   | 4.2<br>4.3 | Balanced response                                |    |

|   | 4.1        | Transistor sizing strategy                       |    |

| т |            | C                                                |    |

| 4 |            | TFB Standard-Cell Design                         |    |

|   | 3.4        |                                                  |    |

|   | 3.4        | 1                                                |    |

|   | 3.4        |                                                  |    |

|   | 3.4        | Auxiliary stages                                 |    |

|   | 3.3<br>3.3 |                                                  |    |

|   | 3.3        | 1                                                |    |

|   | 3.3        | STFB conditional stages                          |    |

|   | 3.2        |                                                  |    |

|   | 3.2        |                                                  |    |

|   | 2.0        |                                                  | 27 |

|      | dix A: SIFB Standard Cen Library           |                    |  |

|------|--------------------------------------------|--------------------|--|

|      | nces<br>dix A: STFB Standard Cell Library  | ndard Call Library |  |

| 7 C  | Conclusions                                |                    |  |

| 6.10 | Test results                               |                    |  |

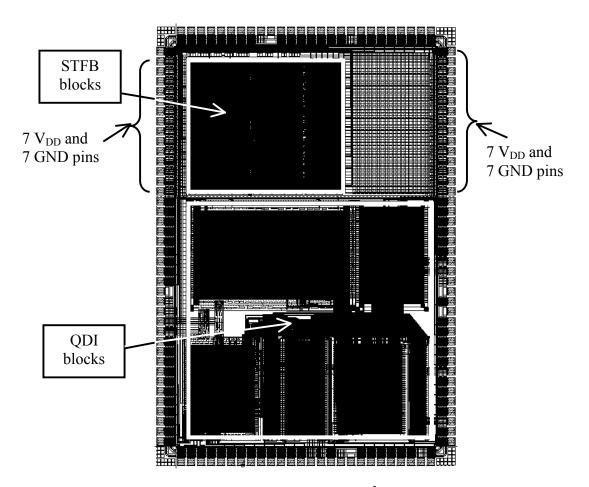

| 6.9  | Demonstration chip implementation and test | 86                 |  |

| 6.8  | Comparisons                                |                    |  |

| 6.7  | Simulation results                         |                    |  |

| 6.6  | Power Distribution and EM                  |                    |  |

| 6.5  | The chip layout                            |                    |  |

| 6.4  | The output circuitry                       | 80                 |  |

| 6.3  | The input circuitry                        |                    |  |

| 6.2  | The Prefix adder                           |                    |  |

## LIST OF FIGURES

| Figure 1 – Synchronous blocks with clock (a) and asynchronous blocks (b)1                      |

|------------------------------------------------------------------------------------------------|

| Figure 2 – Asynchronous circuit design flow under development6                                 |

| Figure 3 - Asynchronous channels10                                                             |

| Figure 4 - Single-track protocol typical connection12                                          |

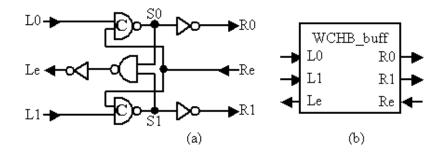

| Figure 5 - QDI WCHB buffer: (a) schematic and (b) symbol13                                     |

| Figure 6 - GasP diagram14                                                                      |

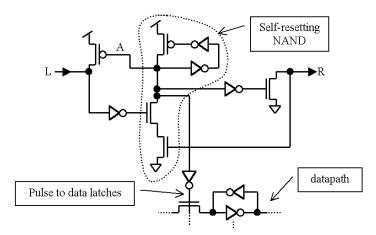

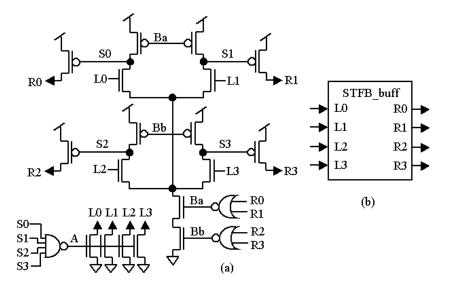

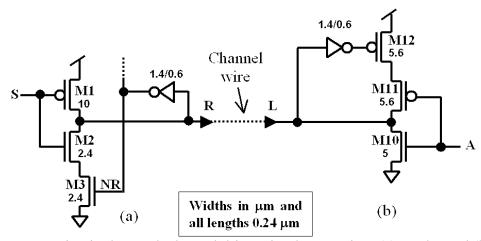

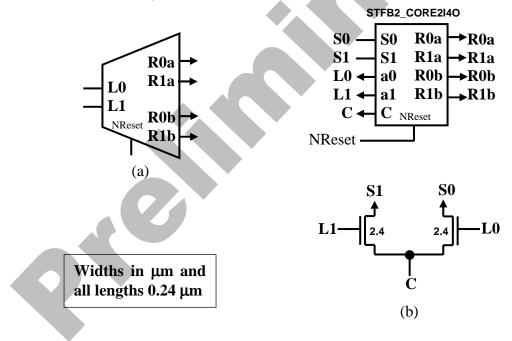

| Figure 7 - 1-of-N STFB buffer: (a) schematic and (d) block diagram18                           |

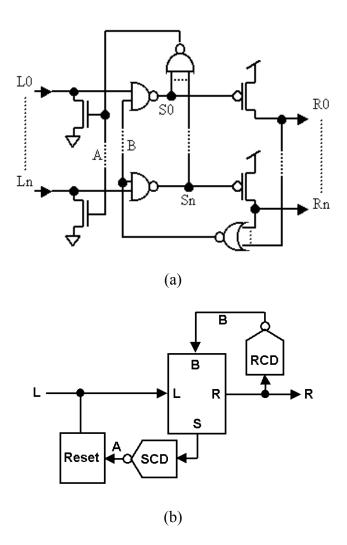

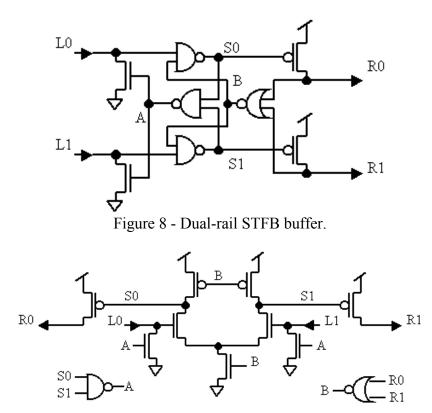

| Figure 8 - Dual-rail STFB buffer19                                                             |

| Figure 9 - Optimized dual-rail STFB buffer19                                                   |

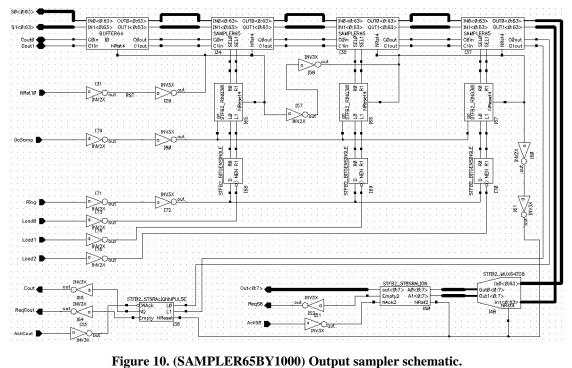

| Figure 10 - Optimized 1-of-4 STFB buffer20                                                     |

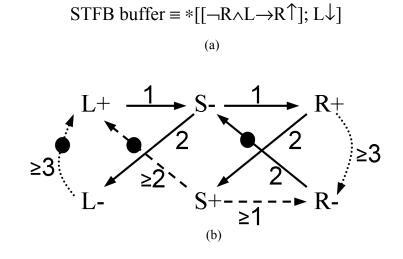

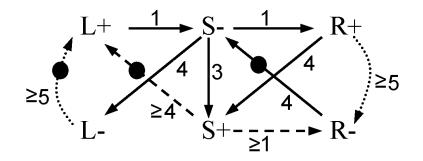

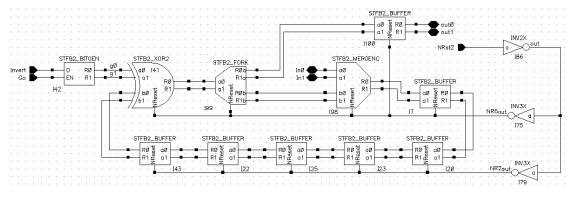

| Figure 11 - STFB buffer: (a) HSE (handshaking expansion) and (b) STG (signal transition graph) |

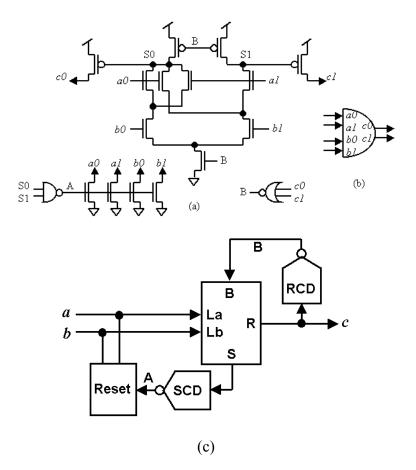

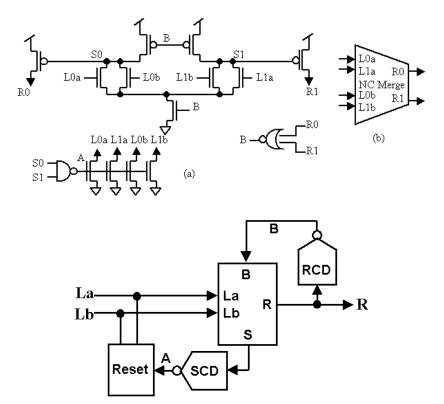

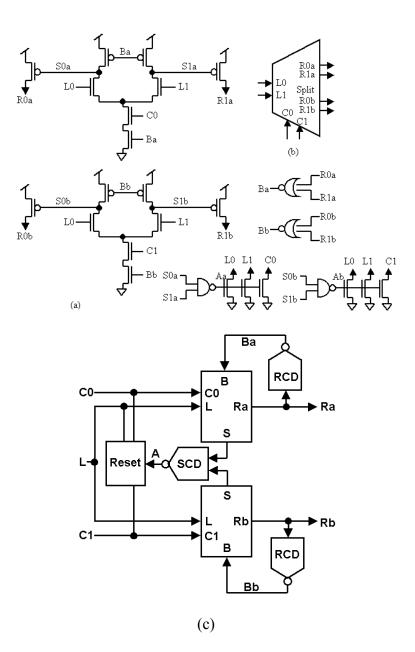

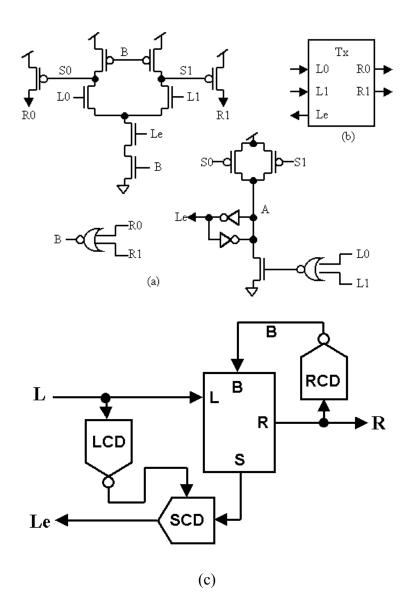

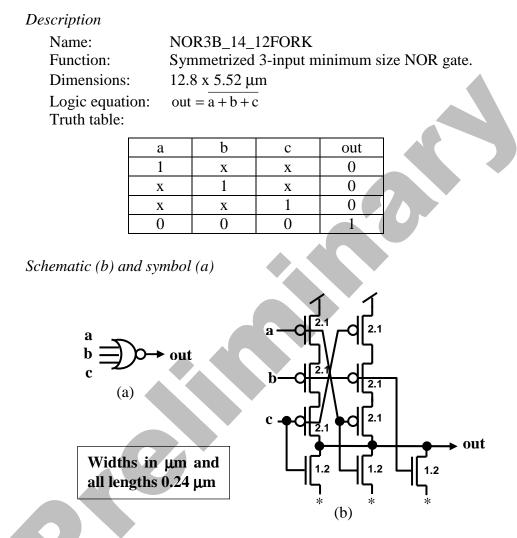

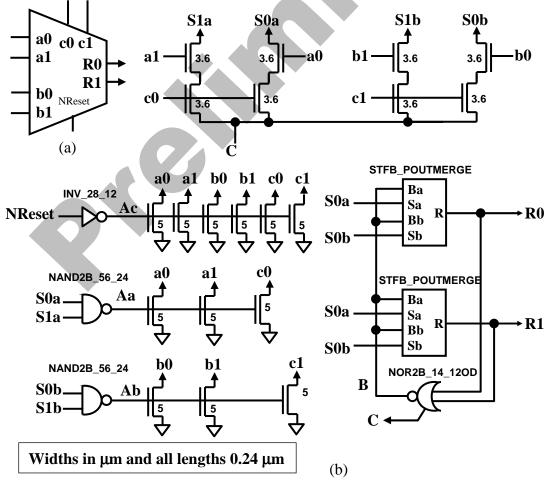

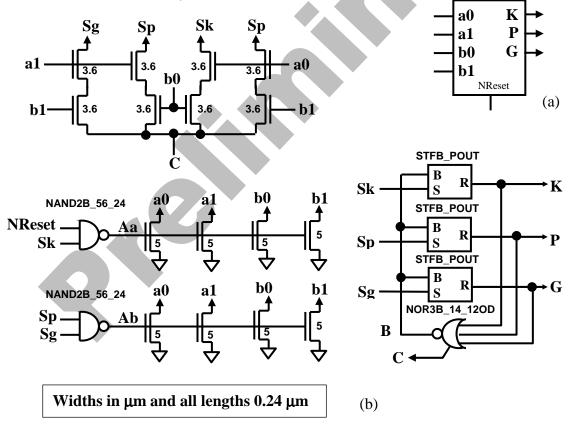

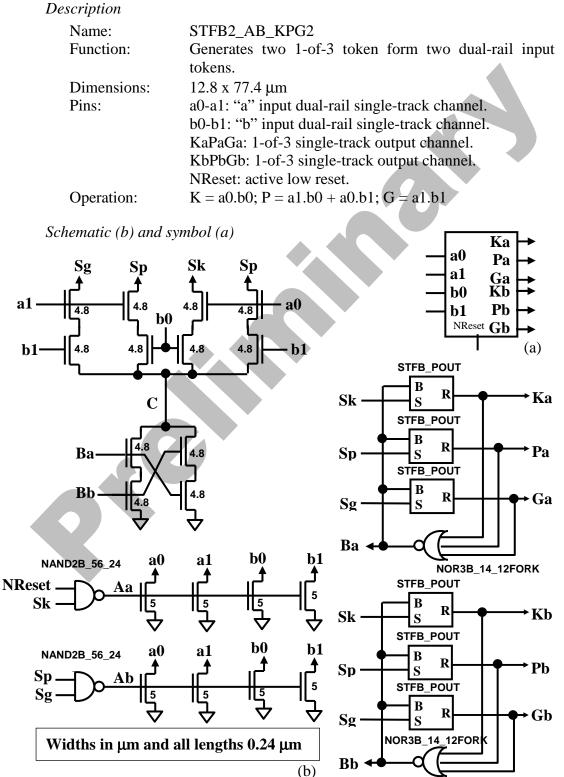

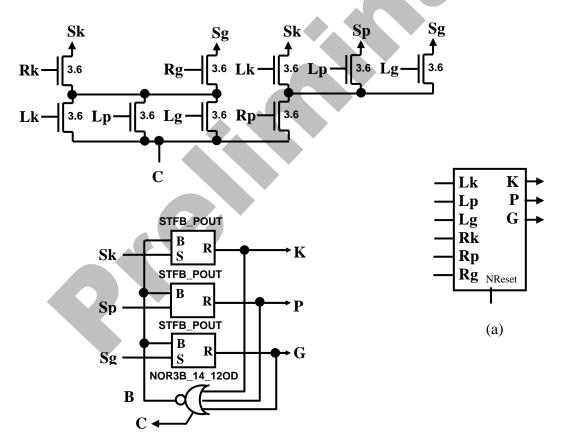

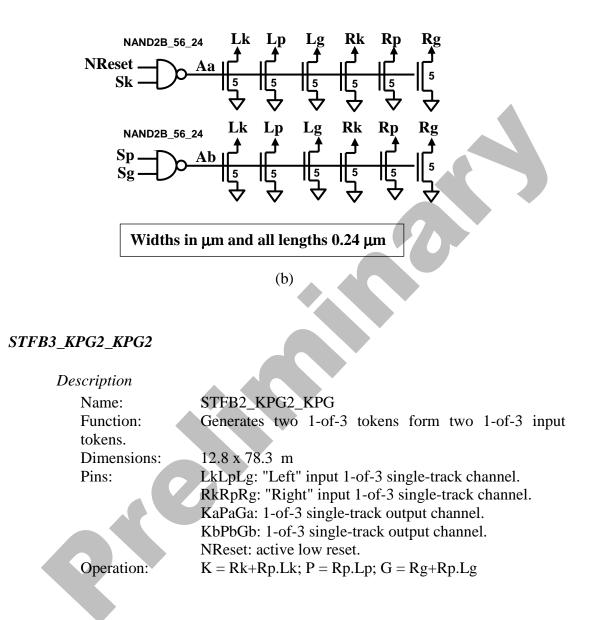

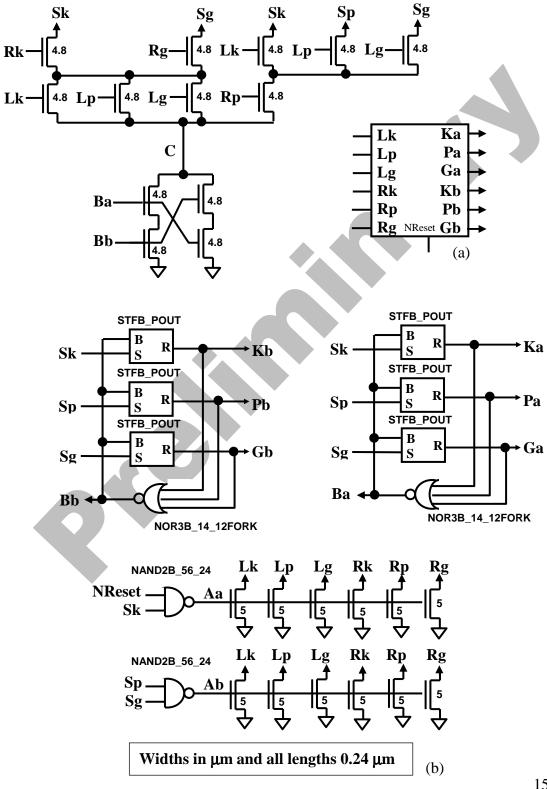

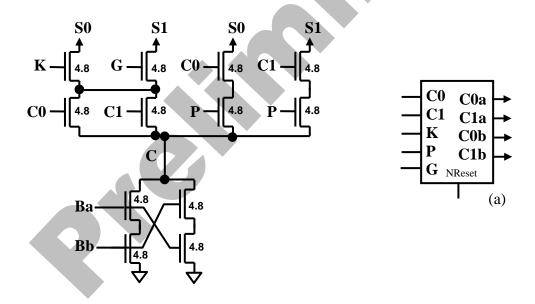

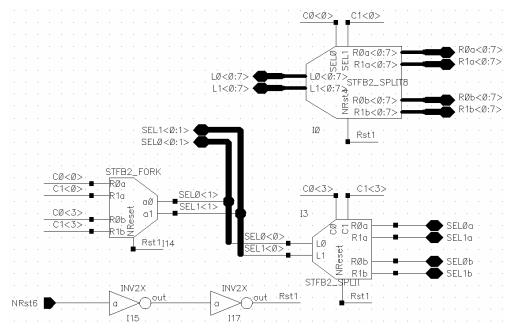

| Figure 12 - SFTB semi-weak-conditioned AND: (a) schematic, (b) symbol, and (c) block diagram23 |

| Figure 13 - Non weak-conditioned STFB AND: (a) schematic, (b) symbol, and (c) block diagram25  |

| Figure 14 - STFB NCMerge: (a) schematic, (b) symbol, and (c) block diagram27                   |

| Figure 15 - STFB copy: (a) schematic, (b) symbol, and (c) block diagram28                      |

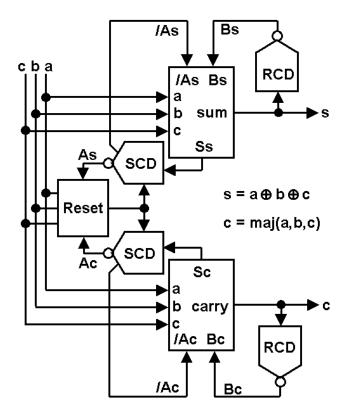

| Figure 16 - STFB FA: (a) XOR and (b) majority gates29                                          |

| Figure 17 - STFB FA acknowledgement circuit30                                                  |

| Figure 18 - STFB FA block diagram30                                                            |

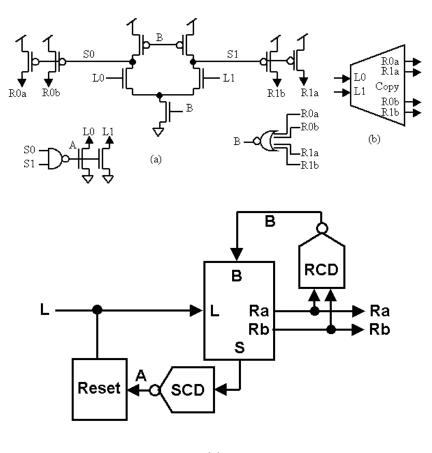

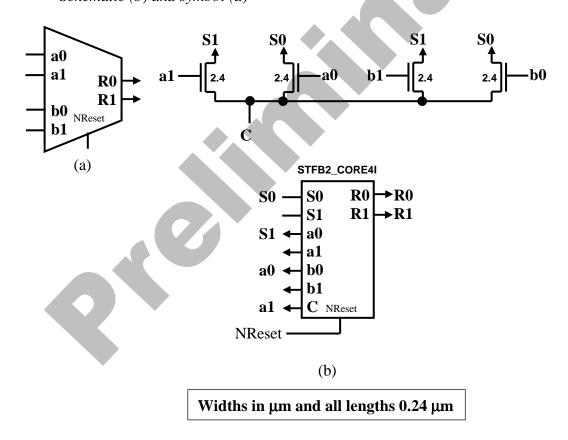

| Figure 19 - STFB split: (a) schematic, (b) symbol, and (c) block diagram32                     |

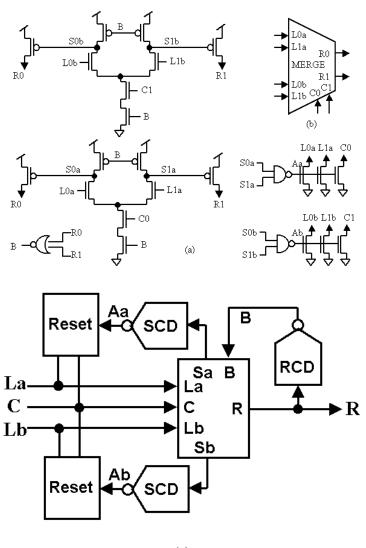

| Figure 20 - STFB Merge: (a) schematic, (b) symbol, and (c) block diagram33                     |

| Figure 21 - STFB 1-bit memory: (a) schematic, (b) symbol, and (c) block<br>diagram                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 22 - STFB Tx: (a) schematic, (b) symbol, and (c) block diagram                                                                                        |

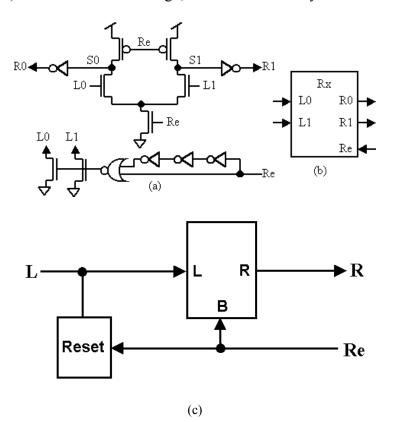

| Figure 23 - STFB Rx: (a) schematic, (b) symbol, and (c) block diagram37                                                                                      |

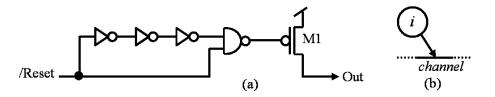

| Figure 24 - STFB bit (a) generator and (b) bucket                                                                                                            |

| Figure 25 - Channel initializer (a) schematic and (b) symbol                                                                                                 |

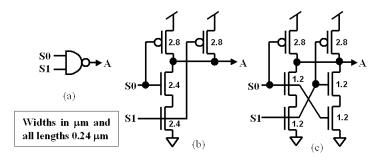

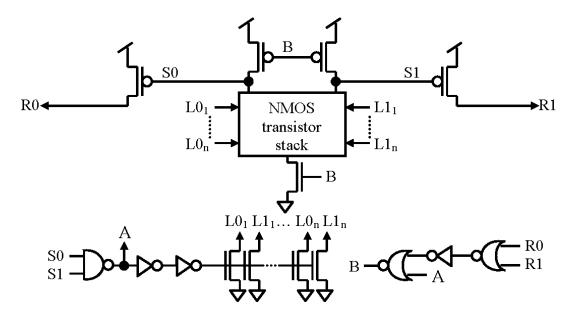

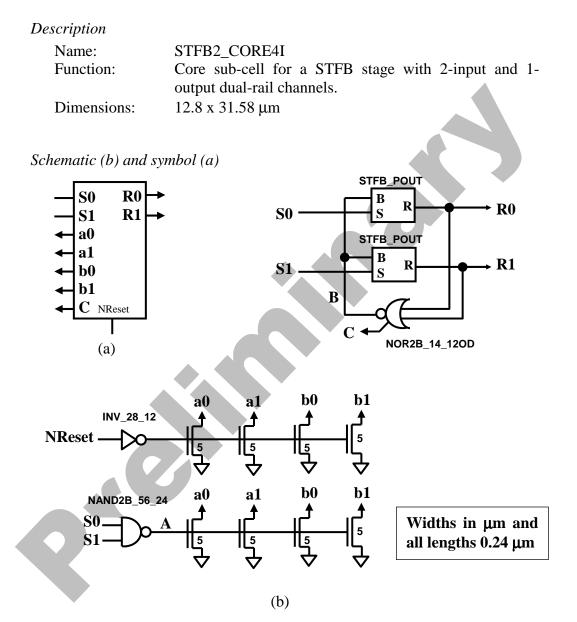

| Figure 26. Sub-cell NAND2B_28_12: (a) symbol, (b) conventional diagram and (c) implemented balanced input diagram42                                          |

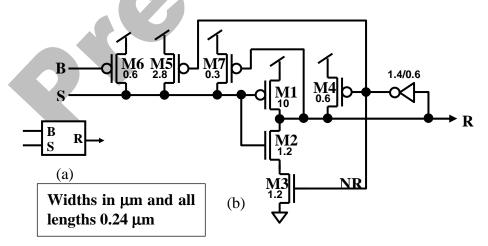

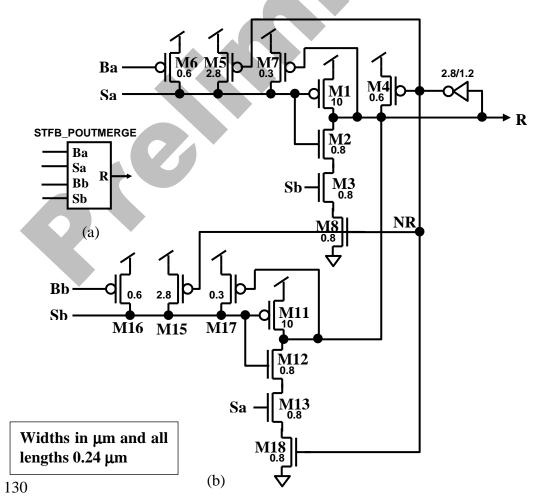

| Figure 27. Sub-cell STFB_POUT (a) block diagram and (b) schematic43                                                                                          |

| Figure 28. B and NR simultaneous activation44                                                                                                                |

| Figure 29. (a) conventional 2-input NOR, (b) balanced RCD and (c) staticizer inverter                                                                        |

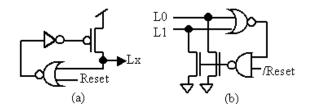

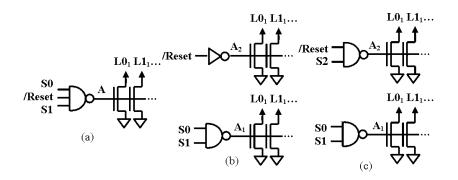

| Figure 30. SCD and reset (a) initially proposed and the implemented (b) 1-of-2<br>and (c) 1-of-346                                                           |

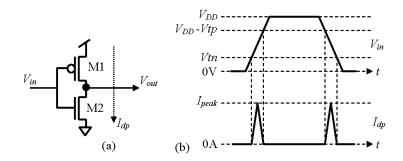

| Figure 31. (a) inverter and (b) direct-path current47                                                                                                        |

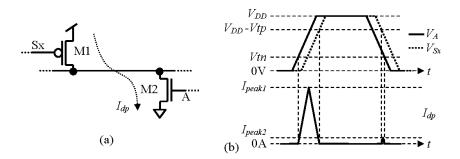

| Figure 32. (a) STFB output/input drivers and (b) direct-path current if $V_A \neq V_{Sx}$ .<br>                                                              |

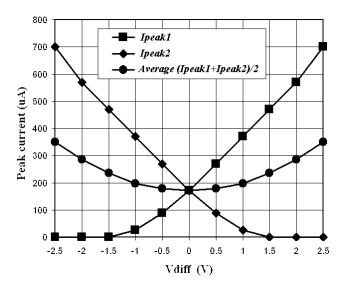

| Figure 33. Peak direct-path current versus the PMOS-NMOS gate voltage difference                                                                             |

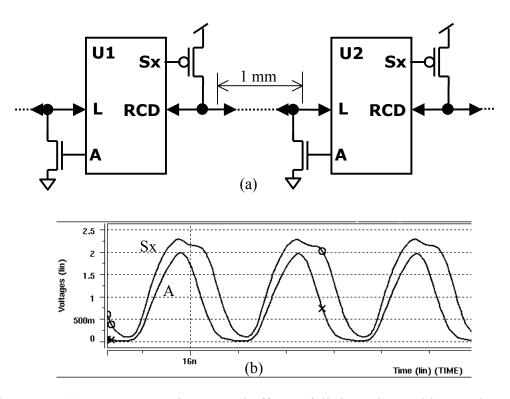

| Figure 34 – (a) Two consecutive STFB buffers at full-throughput with 1mm long wire between them and (b) "Sx" (U1) and "A" (U2) signals ( $V_{DD} = 2.5$ V)49 |

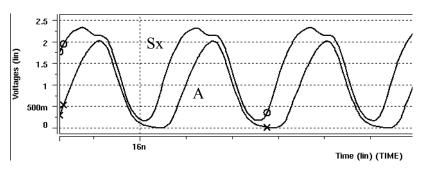

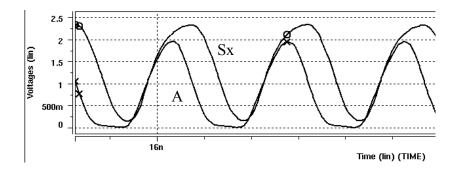

| Figure 35 – Left side stage "Sx" (U0) and "A" (U1) signals with a very short wire between U0 and U1 (V <sub>DD</sub> = 2.5V)                                 |

| Figure 36 - Right side stage "Sx" (U1) and "A" (U0) signals with a very short wire between U1 and U2 ( $V_{DD} = 2.5$ V)                                     |

| Figure 37. 1-of-N Static Single-Track asynchronous channel                                                                                                   |

| Figure 38. Static Single-Track channel drivers implementation: (a) sender and (b) receiver "drive-and-hold" circuits                                         |

| Figure 39 - 10-transistions STFB signal transition graph (STG)60                                                                                             |

| ix                                                                                                                                                           |

| Figure 40 - 10-transitions STFB template60                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------|

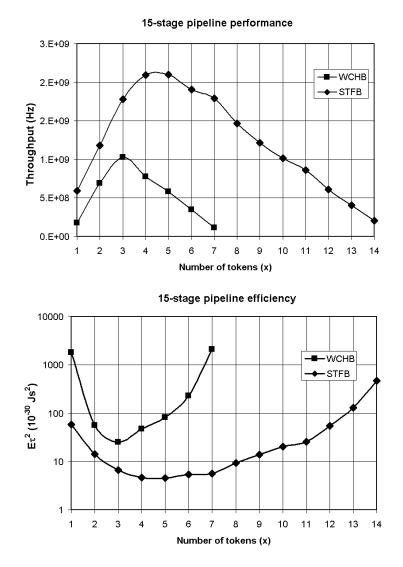

| Figure 41 - Comparison of two 15-buffer pipelines: (top) throughput and (bottom) $E\tau^2$ metric versus pipeline occupancy (x)         |

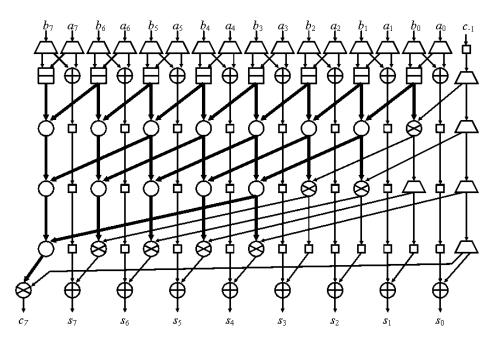

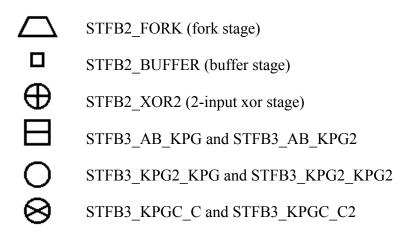

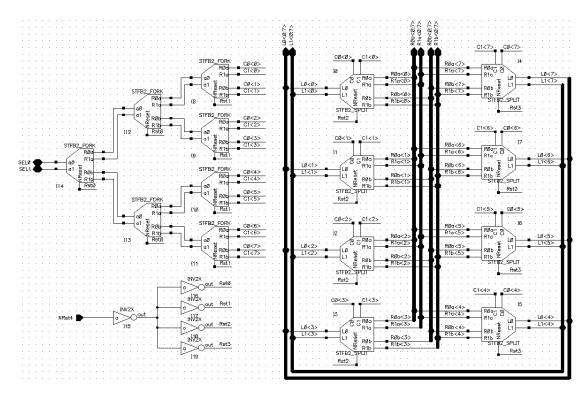

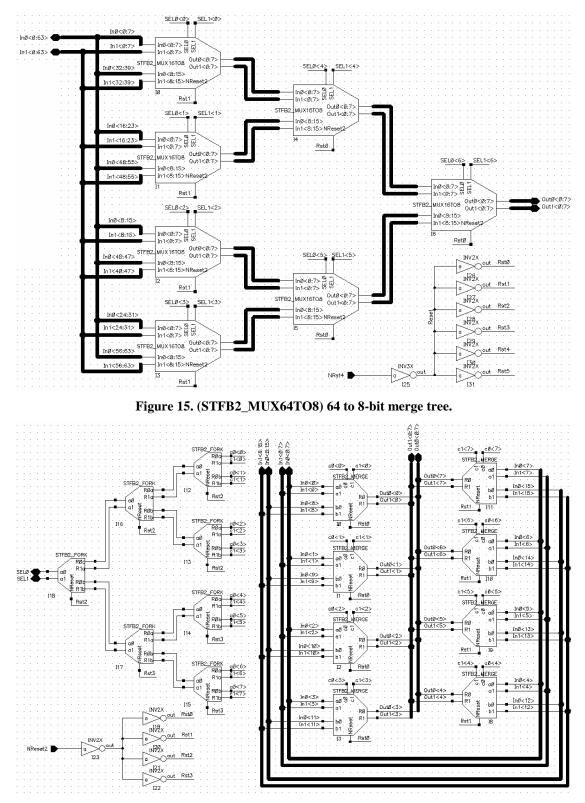

| Figure 42. 8-bit asynchronous prefix adder74                                                                                            |

| Figure 43. Pipeline stages utilized in the adder74                                                                                      |

| Figure 44. 8-bit async. prefix adder optimized75                                                                                        |

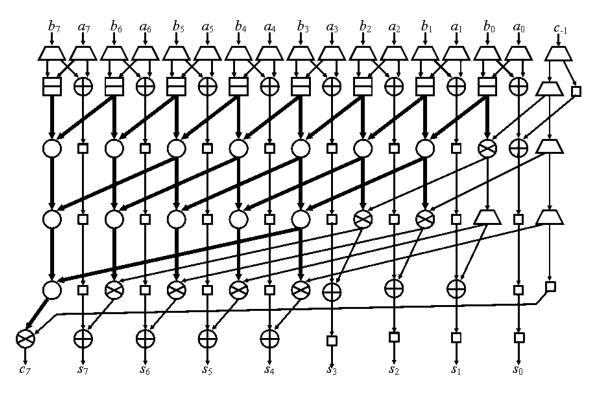

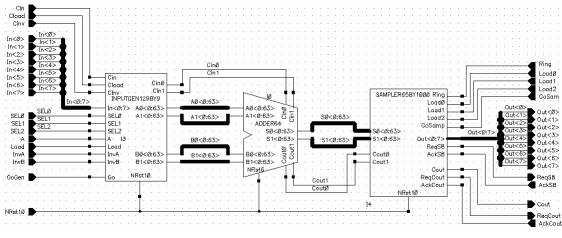

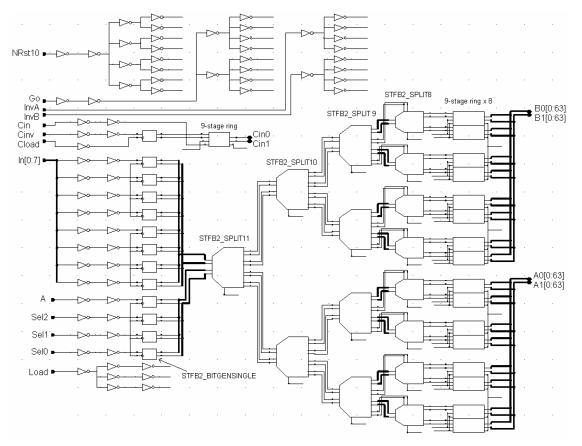

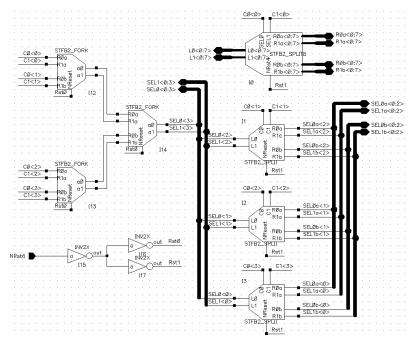

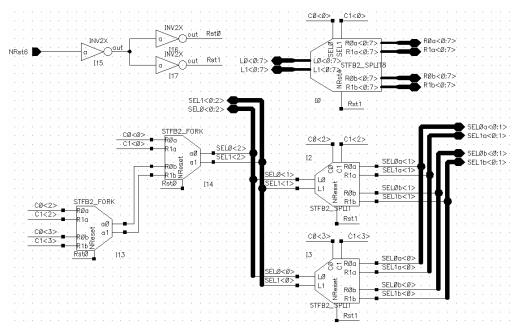

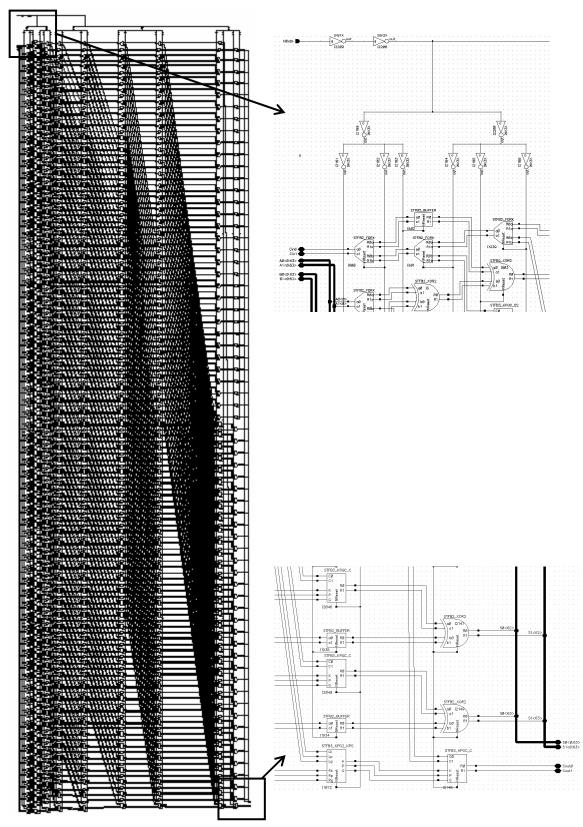

| Figure 45. (a) 64-bit STFB Prefix Adder schematic, (b) input and (c) output details77                                                   |

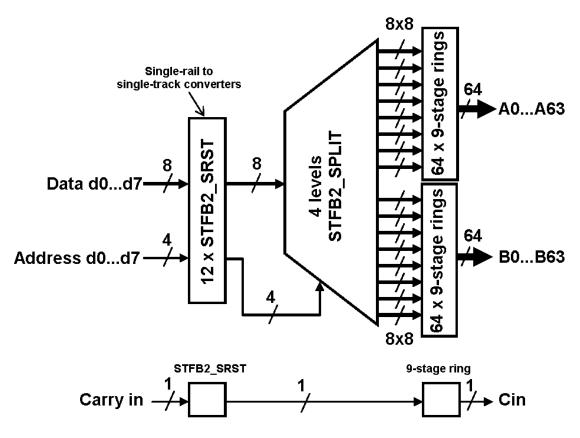

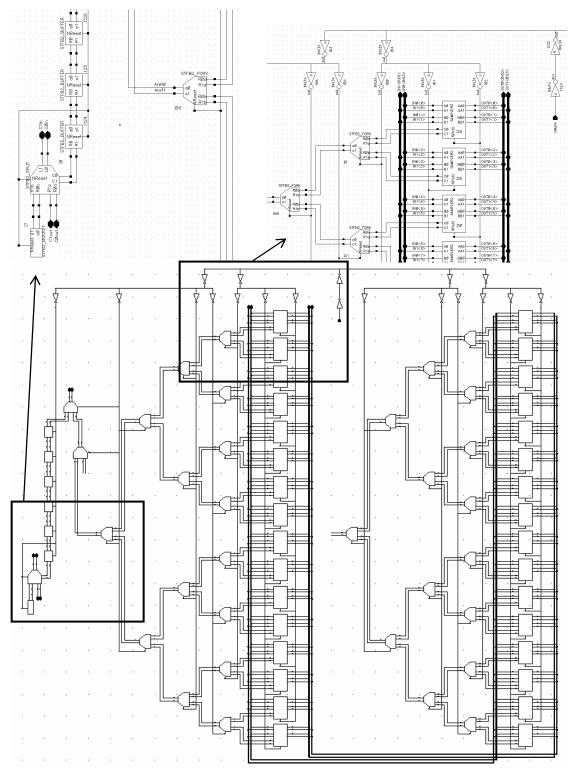

| Figure 46. INPUTGEN129BY9 block diagram79                                                                                               |

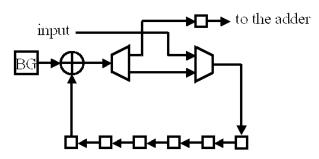

| Figure 47. 9-stage ring utilized in the input circuitry79                                                                               |

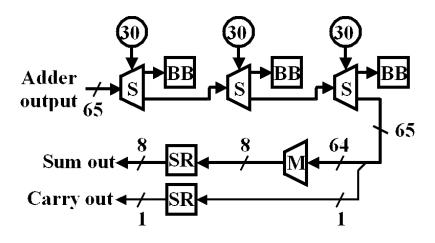

| Figure 48. SAMPLER65BY1000, MUX 64 to 8 and single-rail converters block diagram                                                        |

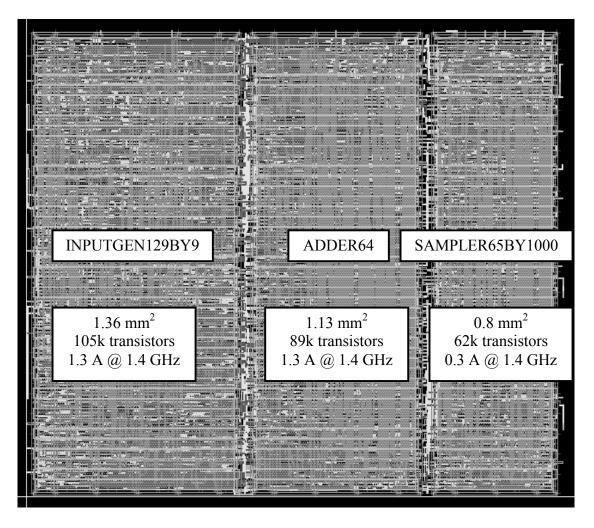

| Figure 49. The input, adder and sampler block layout with respective areas,<br>transistor counts and simulated current and throughput83 |

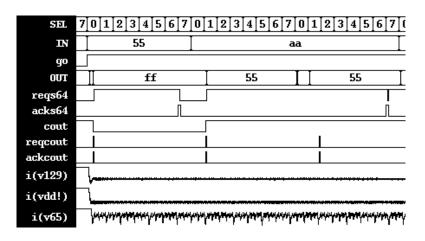

| Figure 50. Typical simulation output84                                                                                                  |

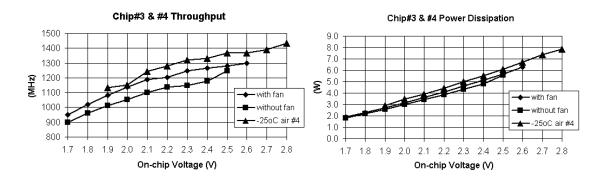

| Figure 51. ASYNC1b layout has 20.5 mm <sup>2</sup> and 132 pins87                                                                       |

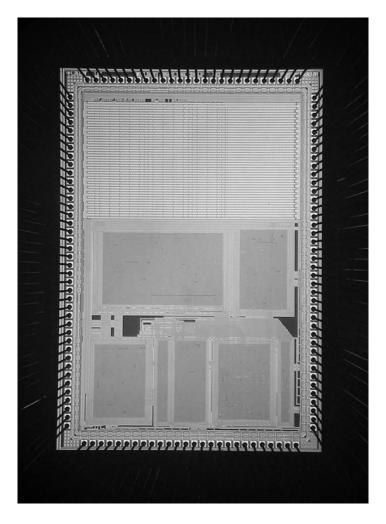

| Figure 52. ASYNC1b demonstration chip (die photo)                                                                                       |

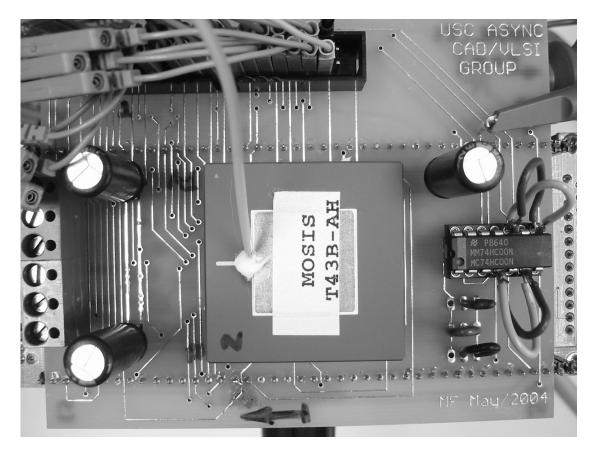

| Figure 53. Demonstration chip on the test board                                                                                         |

| Figure 54. Test chip and equipment setup90                                                                                              |

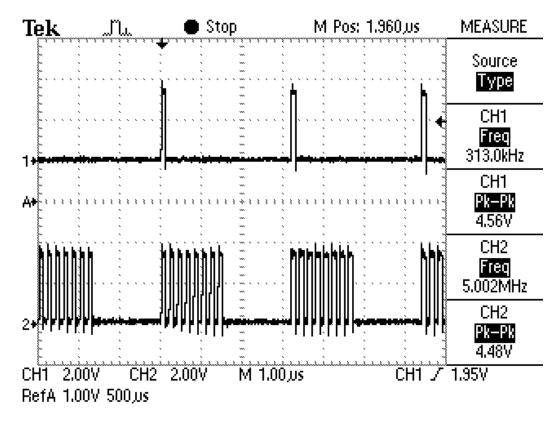

| Figure 55. Chip#3 at 1.25GHz (2.5V on-chip, 2.26A, 40°C package, fan at 1.5").91                                                        |

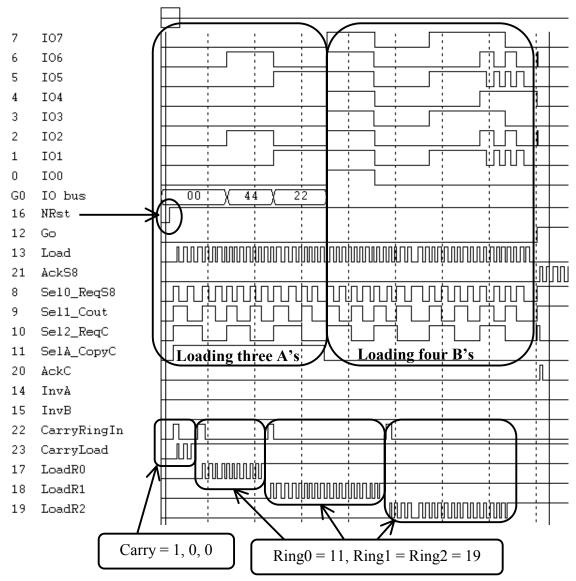

| Figure 56. Logic Analyzer capture wave form of the loading sequence                                                                     |

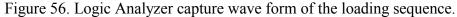

| Figure 57. Logic Analyzer capture wave form of the running mode                                                                         |

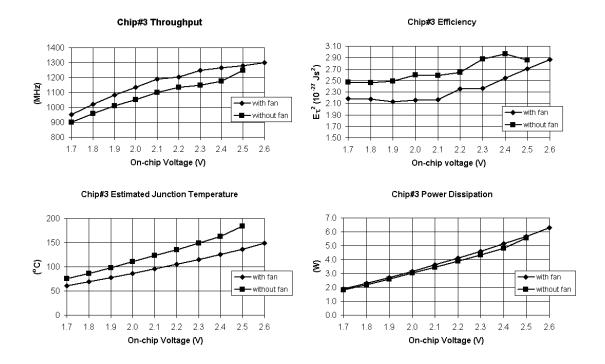

| Figure 58. Graphics of chip #3 measurements95                                                                                           |

| Figure 59. Chip #4 (under -25°C air flow) compared with chip #3 results                                                                 |

# LIST OF TABLES

| Table 1 - Noise source analysis                                              | 53 |

|------------------------------------------------------------------------------|----|

| Table 2. Results                                                             | 85 |

| Table 3. STFB, PCHB and CMOS comparison.                                     | 85 |

| Table 4. Example of loaded operands used for test: sequence 042-F0AF.        | 94 |

| Table 5. Sequence of output results from 042-F0AF test case (sample 1:3971). | 94 |

| Table 6. Measurements of chip #3 with fan at 1.5" distance.                  | 95 |

#### ABSTRACT

This PhD dissertation presents the single-track full-buffer (STFB) templates for a new fast family of fine-grain high-performance asynchronous pipeline building blocks based on the single-track protocol. A demonstration design, implemented using our STFB standard cell library designed for MOSIS TSMC 0.25 µm process, is presented and analyzed. It includes a 64-bit prefix adder and achieves 1.45 GHz.

The STFB template does not require control wires outside of the datapath and the data is 1-of-N encoded. With a forward latency of 2 transitions and a cycle time of only 6 transitions for most of the configurations, the new family can run up to 2 GHz using the MOSIS TSMC 0.25  $\mu$ m process. This is significantly faster than all known quasi-delay-insensitive (QDI) templates and has less timing assumptions than the recently proposed ultra-high-speed GasP bundled-data circuits.

STFB functional blocks can offer three times higher throughput requiring half of the area when compared with QDI circuits. In particular, they are advantageous when the distance between two consecutive data tokens is small, as found in loops with multiple tokens, shared resources or small loops with one token.

The template-based approach makes designing STFB blocks simple. Designing complex pipelined circuits using STFB blocks can use the same flow and cad as any channel-based asynchronous architecture. Physical design may in fact be easier than in QDI-based circuits because there are fewer wires between blocks – i.e., there is no acknowledgement wire. There is one constraint, however, in order to satisfy the timing assumptions, the channel load needs to be bounded and, since the STFB channels are xii

point-to-point connections (no fork in the wires), this bounding is achieved by simply limiting the maximum wire length between STFB pipeline stages.

## **1** INTRODUCTION

As CMOS manufacturing technology scales into deep and ultra-deep sub-micron design, problems with process and within die variations, clock skew, clock distribution, and on-chip communication in high-speed synchronous designs are becoming increasingly difficult to overcome [12], warranting the exploration of alternative design approaches. In particular, asynchronous design is emerging as an increasingly viable alternative.

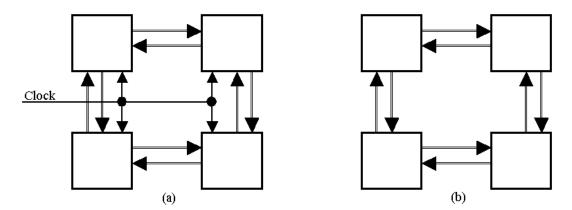

In synchronous design, the clock signal is used to synchronize the state update across the system, while in asynchronous designs, there is no global synchronization and all the blocks are data-driven as shown in Figure 1. The clock signal controls the exact moment when the latches should sample the input data. In order to guarantee that the data is stable when sampled, the clock period should account for the worst-case delay including clock skew and all physical variations.

Figure 1 – Synchronous blocks with clock (a) and asynchronous blocks (b).

#### 1.1 Asynchronous Design

The performance of asynchronous circuits is not limited by any global signal and the activity of each stage is data driven, which facilitates the following advantageous characteristics:

- 1) No clock distribution and no clock skew. Clock skew is defined as the time difference between the occurrence of the real clock edge and the desired clock edge. This difference must be measured and minimized to ensure correct operation and that performance does not significantly suffer. The problems of clock distribution and clock skew minimization are becoming increasingly significant as the technology scales, and within die variations increase, and as more complex system-on-chip (SoC) designs with higher clock frequencies are expected by the market place. The clock distribution network is also responsible for a considerable amount of the consumed power, representing 20–50% of the total power on a chip [36][14] and efforts to reduce its contribution to total power are on-going.

- 2) Low power consumption. Although asynchronous circuits in general have more control overhead, blocks that have no data to process remain completely inactive, providing the equivalent of perfect clock-gating [40]. In particular, clock gating in synchronous circuits is an *ad hoc* method of obtaining the same result and is manageable only at a coarse grain level [33]. Consequently, many asynchronous chips have demonstrated significantly lower dynamic power dissipation than their synchronous counterparts [40][20]. That said, it

should be noted that the problem of increasing static power dissipation due to higher leakage currents in state-of-the-art processes is a common problem to both synchronous and asynchronous circuits and one for which there is active research in both domains.

- 3) Average case performance. The data-driven nature of asynchronous circuits implies that the performance is a function of the data being processed and can be measured as an average over time. In fact, by optimizing for the common case, some asynchronous circuit's average performance can be dramatically higher than its worst-case performance. There are two ways this average case performance may take shape. First, the asynchronous architecture may be designed to take advantage of the input statistics of the data, such as the presence of small numbers. Secondly, the asynchronous physical design may focus on critical cycles in the design and allow longer narrower wires between less critical blocks. In contrast, the synchronous circuit's clock frequency must be adjusted to accommodate the worst-case computation [57][37]. Consequently, some asynchronous circuits have demonstrated significantly better average case performance than the worst-case performance of their synchronous counterparts [37].

- 4) Easing of global timing issues. Moreover, as the technology moves into deep sub micron, wire delays will require several clock cycles to propagate information across the chip and multiple clock domains may need to communicate in a SoC design. Asynchronous interfaces can be used to shell

encapsulate the synchronous blocks and all the communications can be done using latency-insensitive asynchronous channels [7][8].

- 5) Automatic adaptation to physical properties. Synchronous designs have to adjust their clock frequency to cover variations in fabrication process, temperature and power supply. Asynchronous designs, on the other hand, naturally adapt to this conditions and the speed variation in any path will not affect the functionality of the system.

- 6) *Improved EMI*. In synchronous systems, most of the circuit activity occurs around the clock edge, causing a concentration of energy in the clock harmonics. In asynchronous, the activity is uncorrelated, which produces a more distributed noise spectrum with lower peak noise [56]. This characteristic may be very important for SoC and mixed-mode designs.

Among the numerous asynchronous design styles being developed, templatebased fine-grain pipelines have demonstrated very high performance [26][47][34][42][43][44]. Template-based approaches have the advantage of removing the need for generating, optimizing, and verifying specifications for complex distributed controllers, which is both difficult and error-prone [57]. Various templates tradeoff latency, cycle time, and robustness to timing. One of the most robust is the quasi-delay-insensitive (QDI) template proposed by Lines [26]. One of the most aggressive is the ultra-high-speed GasP [47]. GasP offers high throughput but requires a bundled data design style that involves additional timing margins and assumptions that must be verified during physical design and that introduces higher latency through 4

the data path than even the QDI templates, possibly yielding lower system performance.

The single-track full-buffer (STFB) templates presented here and in [18], use 1of-N data encoding and two-dimensional pipelining instead of single-rail encoding and fine-grain pipelining used by GasP. They have two key advantages. First, they remove the GasP bundling constraint, making them easier to design and verify. Second, they reduce forward latency by 58% at the cost of a 26% slower cycle time compared to GasP. The overall performance impact of this tradeoff depends on characteristics of the system. In particular, if the system is latency-critical, where the performance is determined by how fast an individual data token flows through the system, a STFB system can be significantly faster than the comparable GasP system despite having local cycle times that are somewhat larger.

#### 1.2 Test structures

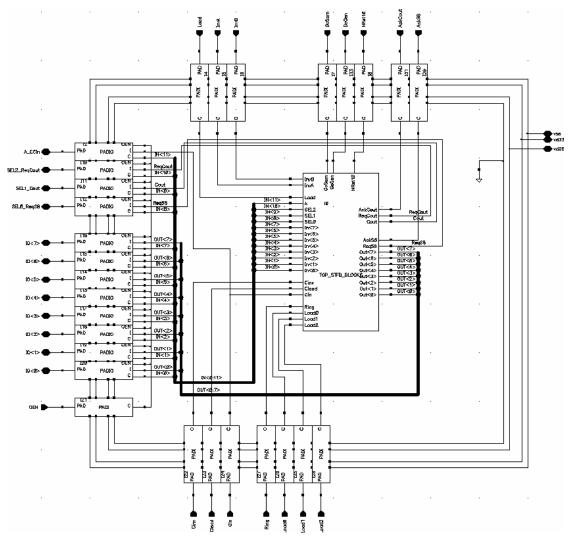

A test chip was designed to validate the design flow as well as the performance of the STFB templates. The central block of the test chip is a 64-bit STFB prefix adder, while the input and output circuitry were designed to feed the adder and sample the results enabling the checking of its performance and correctness at full-throughput.

The input circuit allows loading 129 9-stage rings that are used to continuously feed the adder with two 64-bit operands and one bit carry in. The 64-bit prefix adder structure processes all the inputs simultaneously and generates the 64-bit sum and the carry out with throughput of 1.4GHz. The output circuit is a programmable sampler that forwards results to the pins at manageable rates without slowing down the adder.

#### 1.3 Design flow

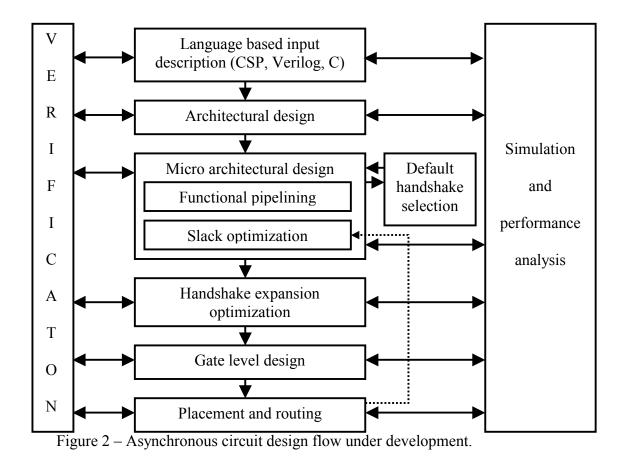

The USC Asynchronous CAD and VLSI group and the Columbia Asynchronous group are working together to define a complete asynchronous circuit design methodology that will offer automated tools for design of both high-performance and low-power asynchronous circuits. The diagram shown in Figure 2 shows the main steps of the design flow. We will be able to start with a language based model, such as CSP [30] and Verilog [10], as the input description of the desired top-level functionality of the chip and may contain information about the constraints on power, energy consumption, throughput, latency, chip area, etc.

In this initial description, however, it is not necessary for the designer to inform any detail regarding internal structure or the specific asynchronous protocols to be used in the circuit under development. The next step, the basic architecture design, identifies the number and relative characteristics of the basic blocks in the design (register files, ALUs, multipliers, etc.). We plan to automate this step by adapting variations in classical high-level synthesis, i.e., scheduling, resource sharing, and binding. In the next step, the micro-architecture design, the designer can choose to implement the architecture with various methods ranging from fine grain pipelines template-based using delay insensitive cells or the STFB templates, presented in this work, to components utilizing bounded delay assumptions with no fine grain pipelining. Once defined the micro-architecture design style, various optimizations can be applied, namely selection of the handshaking protocol, defining the level of pipelining, and slack optimization for pipelined designs. With this micro-architecture, the next step is to identify critical components and perform handshaking optimization to achieve higher performance and lower power. Based on the final micro-architecture, a gate or transistor level design can be generated. This can be done either automatically, using new template-based synthesis techniques that our group is creating, or manually. Finally, placement and routing can be applied basically the same way as for synchronous circuit design. This step may require buffer insertion, due to long wires, which would loop back to slack optimization step in an iterative way.

At every step in the design process, verification and performance analysis tools are used to verify the correct functionality and the overall performance. The focus this work is the generation of new templates for template-based design, as well as to help develop the above CAD frame for the automated design of asynchronous systems.

#### 1.4 Contribution of this work

Our main objective is to present our novel high-performance asynchronous pipeline stages, the Single-Track Full Buffer (STFB) templates, which offers high throughput requiring only 6 to 10 transitions per cycle. To accomplish this we implemented:

- 1) A set of linear and non-linear STFB stages. These templates are freely available through MOSIS Educational Program into a library of standard cells with schematic, layout and symbol views, allowing their easy use (see appendix A).

- 2) Implementation of a demonstration chip. A 64-bit prefix adder and its test structures were designed and implemented, using the MOSIS TSMC 0.25 μm technology, in order to demonstrate the advantage of the small cycle time and modularity offered by the STFB templates as well the flexibility and easy of use of conventional (synchronous) back-end design flow to implement a STFB asynchronous design.

#### 1.5 Organization

The remainder of this work is organized as follows. Section 2 provides relevant background information. Sections 3 and 4 describe our proposed 1-of-N templates in detail. Latency and throughput analysis of STFB buffers with QDI buffers are

compared in Section 5. The demonstration test chip is presented on Section 6 followed by conclusions drawn in Section 7.

## **2 BACKGROUND**

In the absence of the clock, providing global synchronization, masking logic hazards, and signaling the end of each computation step, asynchronous circuits operate using event-driven logic. In particular, asynchronous circuits are often decomposed into processing blocks that communicate data (called *tokens*) through asynchronous channels. This decomposition facilitates re-using asynchronous blocks and simplifies the design of complex systems.

#### 2.1 Asynchronous channels

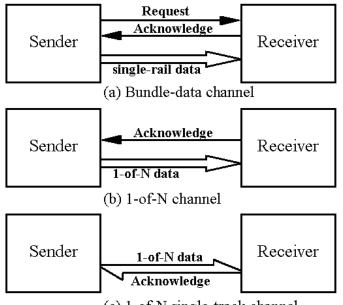

An asynchronous channel is a bundle of wires and a protocol to communicate data across the wires from a sender to a receiver. Figure 3 shows three different types of channels.

(c) 1-of-N single-track channel

Figure 3 - Asynchronous channels.

The bundled-data channel has the advantage that the data is single-rail encoded (the same used in synchronous design) but is dependent on the timing assumption that the data is valid when the request signal is asserted. The request signal is typically driven by a matched delay line that is larger than the sender's computation delay plus some margin.

Alternatively, in a 1-of-N channel, the token value is 1-of-N encoded, meaning that N wires are used to transmit N possible data values by asserting exactly one wire at a time. A *blank* or NULL data is encoded by de-asserting all wires. 1-of-2 (dual-rail) and 1-of-4 encodings are the most common, and both effectively use two wires per bit to encode the data.

In the 1-of-N channel, the receiver detects the presence of the token from the data itself and, once it no longer needs the data, acknowledges the sender. In the typical four-phase protocol, the sender then removes the data by resetting all wires and waits for the acknowledgement to be de-asserted before sending another token.

In the 1-of-N single-track channel, the receiver detects the presence of the token as in the 1-of-N channel but is also responsible for consuming it (by resetting all the wires). The sender detects that the token was consumed before sending another token.

Berkel et al. [3] proposed single-track handshake circuits to control medium-grain bundled-data pipelines. Sutherland et al. [47] later developed faster single-rail GasP circuits to control fine-grain bundled-data pipelines. Nyström [34] recently also proposed a dual-rail (1-of-2) single-track template based on self-resetting pulsed-logic circuits like GasP but which requires significantly more transistors and is significantly slower than STFB.

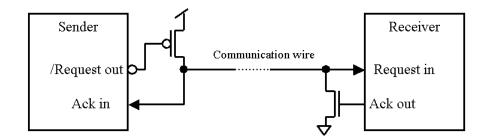

Figure 4 illustrates a single-wire single-track channel. The sender waits for the wire to be low ("ready") before sending a request by driving the wire high ("busy"). After the receiver detects the wire is high and consumes the data, it drives the wire low.

Figure 4 - Single-track protocol typical connection.

Note that "transceivers" can also be implemented using the single-track wire to transport data in both directions if, for every communication event, it is well defined which block will send and which will receive [3]. Similarly, mutually exclusive transmitters and receivers may be connected to the same wire [3]. These possibilities, however, were not covered in our STFB template for the sake of modularity, reliability and performance.

#### 2.2 QDI weak-condition half-buffer (WCHB)

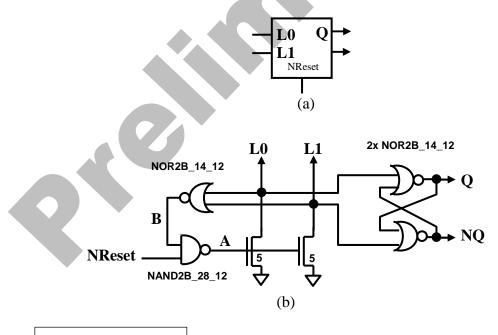

Figure 5 illustrates a well-known dual-rail buffer implementation called weakcondition half-buffer (WCHB) in [26]. L and R identify the left and right environments, 0 and 1 identify the false and the true rails respectively, and "e" identifies the enable signals (high means "ready" and low means "acknowledge"). After reset, L0, L1, R0 and R1 are low while Le and Re are high. Data arrives by one of the left inputs (Lx) rising. This will cause Sx to go low, which will drive the corresponding output Rx high and the left enable Le low. The left environment then will lower Lx while the right environment receives the data Rx and lowers Re. The buffer then raises Le and lowers Rx. The cycle completes when the right environment re-asserts Re. Note that for clarity reset circuitry and staticizers are not typically shown. Note also that the generation and reset of the output token implies that the corresponding input token has been consumed and reset, respectively, a property called weak conditioned in [26] and weak indicatability in [33].

Figure 5 - QDI WCHB buffer: (a) schematic and (b) symbol.

We can derive an estimate of cycle time by counting the number of gate delays or *transitions* in a cycle of operation. The WCHB buffer is faster than other QDI buffers, having a forward latency (fw) of 2 transitions, a backward latency (bw) of 3 transitions and cycle time of only 10 transitions. However, for more complex processing blocks with many inputs, WCHB is not recommended because it generally requires too many stacked PMOS transistors, making it slower than alternative templates.

#### 2.3 GasP bundled data

Figure 6 shows the GasP circuit where, after reset, L, R, and A are high. When L is driven low by the left environment, the self-resetting NAND will fire, driving A low. This will restore L, activate the data latches, and drive R low, propagating the signal and avoiding re-evaluation until after R is restored high by the right environment. The self-resetting NAND will restore itself by driving A high after 3 transitions. The output of the NAND controls the latches in a parallel single-rail datapath.

Figure 6 - GasP diagram.

GasP circuits take 4 transitions to forward data and 2 transitions to reset, i.e., 2 transitions to move a "bubble" (or a "blank") backwards. Of the 4 transitions forward latency, approximately two transitions are required for latency through the latches and satisfying setup/hold times leaving approximately two transitions for computation. Note that the control circuit itself makes up the delay line and that it is the datapath

designer's responsibility to pipeline the datapath to match the control circuit delay while satisfying all setup/hold times and time margin due to process variations.

#### 2.4 Fine-grain vs. two dimensional pipelining

The QDI and GasP templates represent a fundamental dichotomy in pipelining philosophy. The GasP design targets standard datapath widths of, for example, 32-bits. In fact, GasP circuits can be viewed as a complex method of distributing a clock that naturally facilitates gated clocking. Consequently, GasP bundled timing constraint captures many of the same problems as clock distribution and clock skew since it has a global timing assumption that all the 32-bits in the width of the data path will be valid when the request arrives. The QDI templates, on the other hand, are generally applied to small datapaths, say 4 bits, and wider datapaths are made up of a two-dimensional array of communicating blocks [11][28][29]. The motivation of limiting individual QDI templates such as the WCHB to small datapaths is to keep the completion-sensing overhead to a minimum, thereby facilitating reasonable throughput while preserving robustness to timing. For our circuits, as we will see below, it also implies we must guarantee only local timing assumptions, which are easier to test and verify than a wide data-path bundle data constrain.

The completion of a wide datapath, if needed, can be pipelined across several pipeline stages using a technique called pipelined completion sensing [11][28][29]. Similarly, the broadcasting of a control signal affecting the entire datapath can be pipelined to avoid having a large completion tree for the acknowledgement signals. In

this way, two-dimensional pipelines can have a cycle time that is independent of datapath width.

Moreover, the WCHB, along with other QDI templates, generally have significantly lower latency than their GasP template counterparts because they do not suffer from the latch delay and setup/hold times. Replicating the control circuits for each row (slice of bits) of the two-dimensional array, however, may result in increased area and power.

## **3** SINGLE-TRACK FULL-BUFFER CIRCUITS

#### 3.1 STFB buffers

In asynchronous design, buffers are used to balance pipelines for performancedriven *slack matching* [26] or simply storing data. Figure 7 illustrates our 1-of-N STFB buffer template and its block diagram. When one of the n inputs (Lx) is driven high by the left environment, the corresponding NAND gate will drive Sx low, thereby driving both the corresponding Rx and "A" (the "Acknowledgement" signal) high. "A" going high causes Lx to reset low, enabling the left environment to send a new token. Meanwhile, Rx going high causes the "B" ("**B**usy") signal to lower, restoring Sx high and preventing the NANDs to re-fire even if a new token arrives. The restoring of Sx, in turn, resets "A". The cycle completes when the right environment lowers Rx, resetting "B" low, and allowing a new data token to be processed. Since distinct tokens can simultaneously be at the left and right environments, the template is said to be a full buffer and have capacity (slack) of 1 token per buffer.

Figure 7 - 1-of-N STFB buffer: (a) schematic and (d) block diagram.

As shown in the block diagram, the gate that drives "A" (Acknowledge) is called SCD (State Completion Detector) because it detects that the internal state of the template has captured the input token. The gate that drives "B" is called RCD (Right Completion Detector) because it detects that the output token has been sent to the right environment. The SCD is responsible for the reset of the input token and the RCD enables the main block to operate when the output channel is clear. Note that the generation of the output token *indicates* [30][48] that the corresponding input token was valid and consumed. However, the reset of output tokens is caused by the right environment and does not indicate that the input tokens have reset. Consequently, we call the STFB buffer, along with most STFB logic templates, *semi-weak-conditioned*. As such, there is a timing assumption that the template must reset the input channel before "A" is de-asserted.

Figure 8 shows, as an example, a dual-rail STFB buffer. Figure 9 shows an optimized version in which the static NAND gates driving S0 and S1 are merged into one dual-rail dynamic gate that is reset only by the "B" signal. Figure 10 shows a similarly optimized 1-of-4 STFB buffer circuit and symbol.

Figure 9 - Optimized dual-rail STFB buffer.

Figure 10 - Optimized 1-of-4 STFB buffer.

STFB buffers have a cycle time of 6 transitions. This is 40% faster than WCHB and the same as GasP. The latency is 2 transitions, which is the same as WCHB and half that of GasP.

The STFB buffer, however, has higher complexity than both WCHB and GasP buffers. Compared to WCHB buffer, including required staticizers and reset circuit [26], the STFB buffer has 7 more transistors. This increased complexity, however, is mitigated by the fact that the proposed STFB buffer is a full buffer (i.e., has slack of 1), while WCHB is a half buffer (slack of ½). Moreover, the STFB buffer does not require the acknowledge wires (Le/Re), which may represent a significant saving in area and routing effort, and allow the implementation of more complex functions,

which would require to move to PCHB since WCHB is used only for buffers. In addition, the power consumption per communication of STFB buffer is potentially lower than WCHB buffer since each communication requires half the number of wire transitions.

Compared to a GasP buffer with a standard 32-bit datapath, the area and power consumption of a STFB pipeline may be higher because the two-dimensional STFB pipeline will be made up of many buffers in parallel and each buffer will have its control circuit overhead.

Figure 11 shows the handshaking expansion (HSE) equation and the signal transition graph (STG) for the presented buffers. The notation "+", " $\uparrow$ " and "-", " $\downarrow$ " represent the rising and falling of the signals respectively. The left and right environments drive the dotted arrows and the dashed arrows represent timing constraints. The arrows are annotated with delays in terms of transitions. The greater than or equal sign (" ") reflects a timing assumption, which states that the separation between identified events is at least the specified number of transitions.

21

# Figure 11 - STFB buffer: (a) HSE (handshaking expansion) and (b) STG (signal transition graph).

As can be deduced from the STG, the STFB buffer has somewhat tight timing constraints. In particular, the timing margin between the tri-stating of an output wire (one transition after S+) and the earliest time the environment can reset the wire (R-) is zero. Moreover, the timing margin between tri-stating of an input wire (two transitions after S+) and the earliest time the left environment can drive the wire (L+) is also zero. In particular, if these margins are violated, significant short circuit current may occur during the transitioning of the line. In addition, it is assumed that three transitions are sufficient to fully discharge/charge a line. To accommodate these constrains, the channel load needs to be bounded. This is achieved by limiting the wire length of the channels, which can be easily verified after the placement and routing phase. Moreover, automated static timing analysis tools are under development to further improve the design robustness and sign-off process. Unless otherwise noted, these timing constraints apply to all subsequent examples.

#### 3.2 STFB forks and joins

This section covers a variety of non-linear pipelines stages that involve multiple input and/or multiple output channels and can perform more complex logic functions. While we focus on two dual-rail (1-of-2) inputs/outputs, templates that handle more channels and/or 1-of-N encoding are natural extensions.

### 3.2.1 Dual-rail STFB semi-weak-conditioned AND

Figure 12 illustrates an STFB AND stage and its block diagram that performs c = a\*b, where *a* and *b* are dual-rail single-track inputs and *c* is the dual-rail single-track output.

Figure 12 - SFTB semi-weak-conditioned AND: (a) schematic, (b) symbol, and (c) block diagram.

All the inputs are "acknowledged" by the signal "A" as soon as S0 or S1 goes low. For S1, this happens when a1 and b1 are high. For S0, a0 or b0 driven low is sufficient to define the logic result, but the circuit explicitly waits for one of the three input combinations 00, 01, and 10 to arrive before lowering S0. In this way, the evaluation of S0 also implies that both tokens (a and b) arrived, guaranteeing that the acknowledgement does not precede the arrival of a late token, making this gate semi-weak-conditioned.

#### 3.2.2 Dual-rail STFB non weak-conditioned AND

Figure 13 shows a non weak-conditioned AND stage and its block diagram. This circuit generates a zero result token as soon as one of the inputs is zero even if the other input has not arrived. When all the inputs are finally present, however, the stage sends an acknowledgement to all inputs.

Figure 13 - Non weak-conditioned STFB AND: (a) schematic, (b) symbol, and (c) block diagram.

To do this, while forwarding the early zero result, the gate's SCD (State Completion Detector) sets "A" high, which will disable the logic for future evaluations by keeping "/A" low and will hold the information that an acknowledge is pending. When the LCD (Left environment Completion Detector) detects that all input tokens are present, the acknowledge signal is passed to the transistors that will

"consume" the data at the inputs and "A" is reset to zero. This will restore "/A" high and the gate will be ready to evaluate again. This LCD structure adds two transitions to the cycle time but loosens the timing margin between S- and resetting the inputs (corresponding to L- in Figure 11) by two gate delays.

Notice that for multiple inputs, this gate has a much simpler NMOS transistor stack than the weak-conditioned STFB AND.

#### 3.2.3 Dual-rail STFB OR and STFB XORs

By re-arranging the transistors in the evaluation stack (main block), different logic functions may be implemented within the STFB template. A dual-rail STFB OR performs the logic operation: c = a+b, where a and b are dual-rail single-track inputs and c is the dual-rail single-track output. This function can be implemented either with semi-weak-conditioned logic or with non-weak-conditioned logic simply by rearranging the transistors in the NMOS stack of the AND circuits presented in Section 3.2.1 and 3.2.2.

Similarly, the dual-rail STFB XOR performs the logic operation:  $c = a \oplus b$ , where *a* and *b* are dual-rail single-track inputs and *c* is the dual-rail single-track output. The STFB XOR, however, must be semi-weak-conditioned, because, for any XOR gate, all input token values must be known before the output value could be computed.

#### 3.2.4 Dual-rail STFB non-conditional merge

The non-conditional merge operation concatenates the incoming data from different mutually exclusive input channels. Figure 14 shows a 2-to-1 non-conditional merge circuit, symbol, and block diagram.

Figure 14 - STFB NCMerge: (a) schematic, (b) symbol, and (c) block diagram.

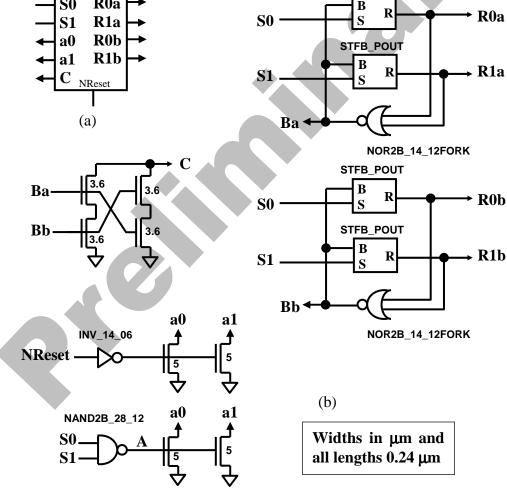

## 3.2.5 Dual-rail STFB fork

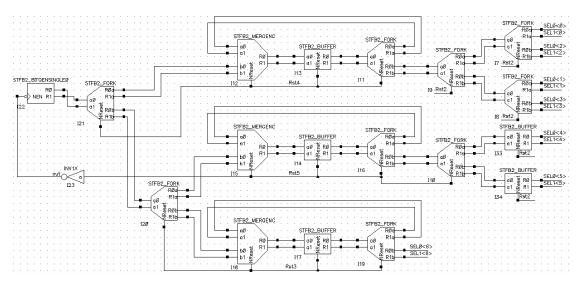

The fork operation consists of replicating the incoming data to several different paths if all output paths are ready. Otherwise, the input data must wait.

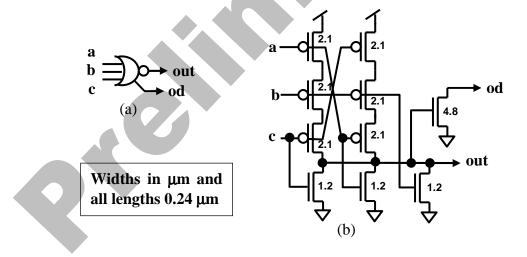

Figure 15 shows the 1-to-2 fork stage. Notice that the four-input NOR gate (with a stack of four PMOS transistors) driving B slows down the STFB fork performance. To speed-up the B signal, however, we can use 2 two-input NOR gates to generate Ba

and Bb, and replace the B NMOS transistors with stacked Ba and Bb NMOS transistors (similar to what is shown in Figure 10).

(c)

Figure 15 - STFB copy: (a) schematic, (b) symbol, and (c) block diagram.

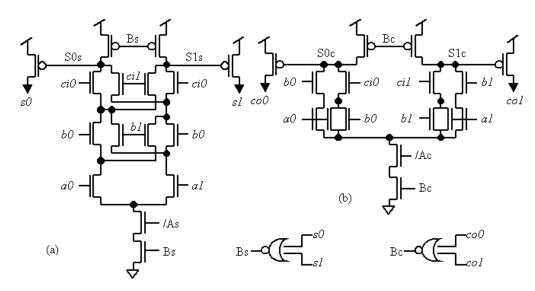

## 3.2.6 Dual-rail STFB full adder

This is an example of STFB computational stage. To implement a full adder (STFB FA) we need to compute the sum and the carry out before resetting the inputs. As illustrated in Figure 16 and Figure 17, this can be done with a three-input XOR and a three input majority (MAJ) gate. The XOR generates the sum (s=a+b+ci) and the

MAJ generates the carry out (*co*=MAJ(*a*,*b*,*ci*)). Figure 18 shows the block diagram of the STFB FA.

In this structure, the carry evaluates as soon as enough inputs arrive to define the correct output value but the acknowledgement waits for both outputs to be generated which, because the sum is an XOR gate, implicitly means that all inputs have arrived. Note that the acknowledgement circuitry adds two gate delays to the cycle time but also loosens the timing margin between S- and resetting the inputs by two gates.

Figure 16 - STFB FA: (a) XOR and (b) majority gates.

The long nmos stacks in the sum and carry circuits can be reduced by one transistor by removing the transistors controlled by /As and /Ac and making As and Ac new inputs of their respective RCD NOR gates.

Figure 17 - STFB FA acknowledgement circuit.

Figure 18 - STFB FA block diagram.

# 3.3 STFB conditional stages

This Section covers a variety of stages in which input and/or output channels are conditionally read or written.

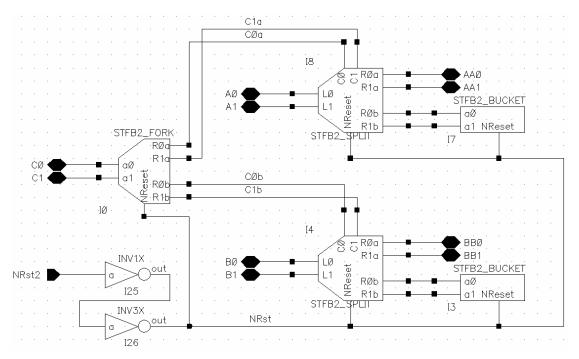

#### 3.3.1 Dual-rail STFB split

The split operation consists of forwarding incoming tokens to one of two output channels based on the value of a control (C) channel. If the chosen output path is busy, the data must wait. Note that the micropipeline version of this block, which samples the control signal rather than consuming it, is called a *select* [46].

Figure 19 shows the 1-to-2 STFB split circuit, symbol, and block diagram. In this example, when C is low (C0 = 1), L is directed to Ra and, when C is high (C1 = 1), to Rb. Interestingly, the STFB split allows a token to be forwarded to one channel even if the other channel is busy (each output has its own RCD), which increases the degree of parallelism.

Figure 19 - STFB split: (a) schematic, (b) symbol, and (c) block diagram.

## 3.3.2 Dual-rail STFB merge

The merge operation consists of choosing one of the incoming tokens based on the value of a control (C) input. If the output path is busy, the input and control tokens must wait. After forwarding the data, the control token is also consumed.

(c)

Figure 20 - STFB Merge: (a) schematic, (b) symbol, and (c) block diagram.

Figure 20 shows the 2-to-1 merge circuit, symbol, and block diagram. When C is low (C0 = 1), La is directed to R and, when C is high (C1 = 1), Lb is directed to R.

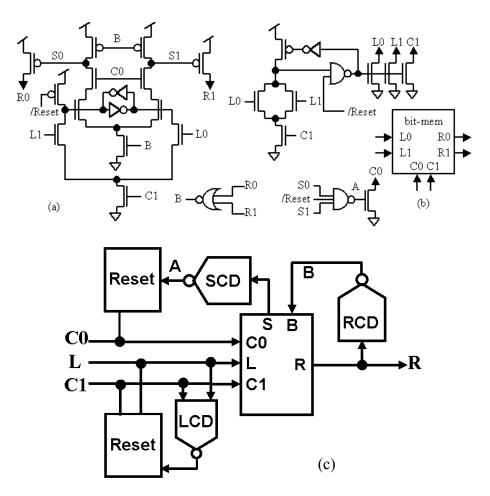

#### 3.3.3 Dual-rail STFB one bit memory

Figure 21 shows a STFB one-bit memory stage. The circuit of has a static memory unit (two inverters), an input (L), an output (R), and a control channel (C). If

the control input is low (C0=1), the memory content is transferred to the output (R) and C0 is consumed. If the control input is high (C1=1), the memory is written with the L input value and both, C1 and L, are consumed.

Figure 21 - STFB 1-bit memory: (a) schematic, (b) symbol, and (c) block diagram.

Notice that the control signal flows only trough the channel C, which guarantees the read and write operations are executed in the requested order. Also, there is a timing assumption that the 3 transitions of the write operation are long enough to set the memory value.

#### 3.4 Auxiliary stages

This Section covers bit generators used to generate a stream of tokens, bit buckets to consume unwanted tokens, converters between single-track and four-phase protocols, and staticizer/reset circuitry.

### 3.4.1 Four-phase to STFB converters

The "transmitter" circuit, illustrated in Figure 22, is our proposed interface between four-phase asynchronous logic and STFB. In this circuit, if Le is high and the right environment is ready, a data arriving from the left environment will be transmitted to the right environment and the signal Le will be set low. This also disables the buffer, avoiding re-transmitting the same data after the right environment consumes it. Le will remain low until both inputs return to zero (four-phase protocol). When this happens, Le is set high and the transmitter is ready for the next data.

Figure 22 - STFB Tx: (a) schematic, (b) symbol, and (c) block diagram

The "receiver" circuit, illustrated in Figure 23, is our proposed interface between STFB and four-phase asynchronous logic. In this circuit, if Re is high (the right environment is ready), a data from the left environment will be received and the buffer will wait for the signal Re to be set low. When Re goes low, a three gate-delay pulse is generated to consume the left environment data and the receiver is reset (R0 and R1

goes low). While Re is low, R0 and R1 are reset and no new data is received (fourphase protocol). When Re returns to high, the receiver is ready for the next data.

Figure 23 - STFB Rx: (a) schematic, (b) symbol, and (c) block diagram.

The cycle time of these converters is 10 transitions when connected to WCHB buffers, which matches the WCHB buffer cycle time.

### 3.4.2 Dual-rail STFB bit generators and bit buckets

A bit generator creates a data token every time the line is empty, while a bit bucket consumes unwanted tokens. Both are also useful in test circuitry. The proposed STFB bit generator and bit bucket are shown in Figure 24.

Figure 24 - STFB bit (a) generator and (b) bucket.

## 3.4.3 Channel initializer

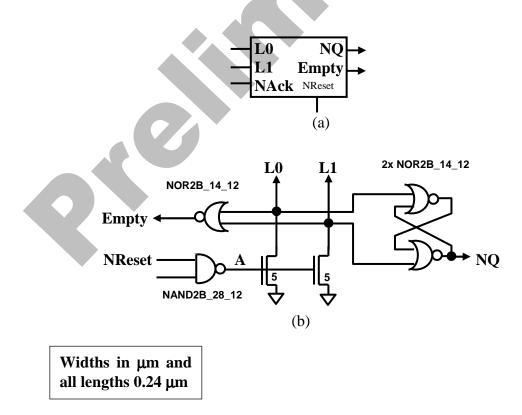

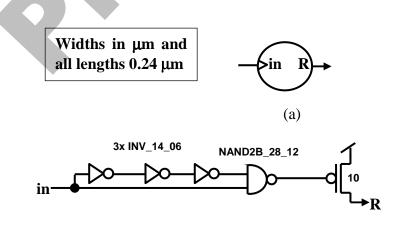

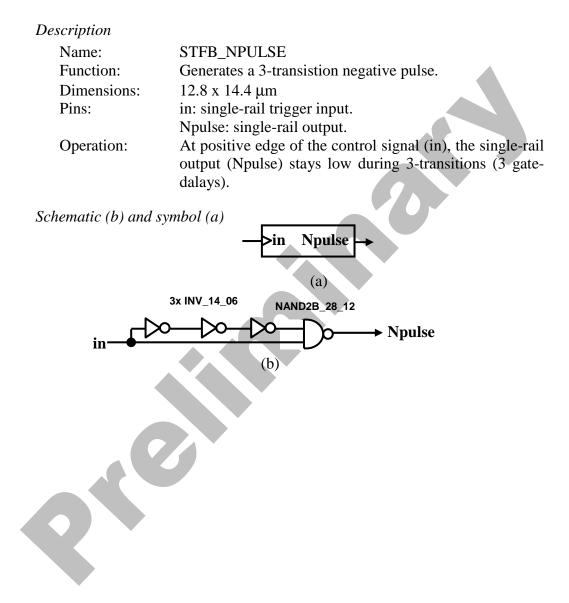

Some circuits, such as loops, may require some form of initialization that cannot be done by a bit generator since it is required just once. One approach is to modify the pipeline stage that needs to be initialized and, instead of simply reset the input wires during the reset phase, place a valid token at its input. This requires a new design and layout of that stage. Another approach is to use an external drive circuit to pull a wire up during a short 3 transitions to "inject" a token in the line after the /Reset signal is deasserted (rise edge of the /Reset signal). Figure 25 shows our channel initializer circuit and symbol. It is an edge to pulse converter with open-drain PMOS driver. The value *i* represents the injected value in the channel after reset.

Figure 25 - Channel initializer (a) schematic and (b) symbol.

Since the STFB stages are very fast, we must take care not to use the channel initializer in two consecutive channels to avoid one token overrunning the other. Rather, for neighboring channels that require initialization, we propose to use modified stages.

Another approach is to add a non-conditional merge stage in the pipeline, by replacing a buffer for example, with one input connected to the pipeline and use to other input to insert the initialization tokens we want. This method was used in our demonstration design as described below.

# 4 STFB STANDARD-CELL DESIGN

In this chapter we present a number of implementation issues of the STFB standard-cell design. Due to the timing assumptions in the STFB template, the transistor level design of each cell and sub-cell was done manually and checked through extensive SPICE simulation as described below.

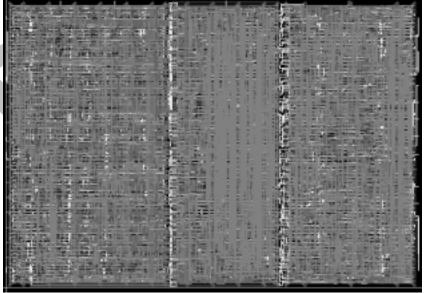

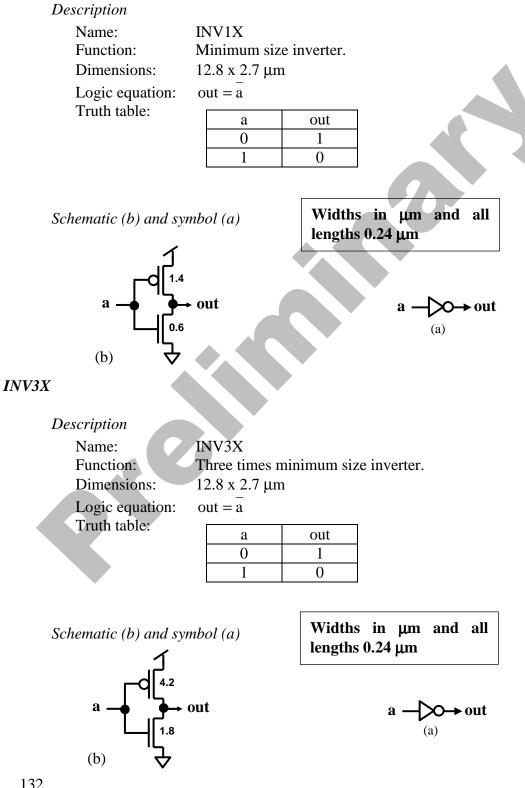

#### 4.1 Transistor sizing strategy

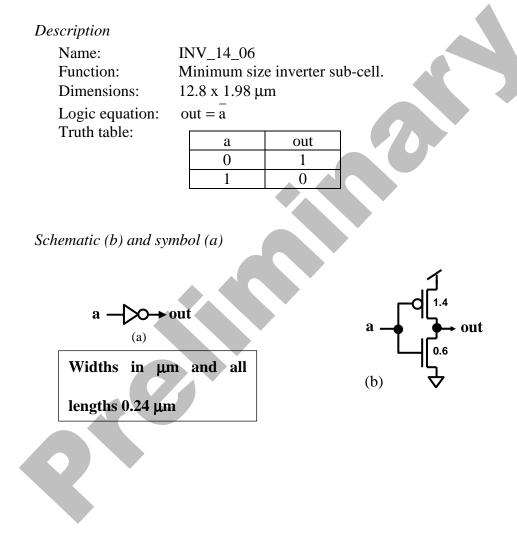

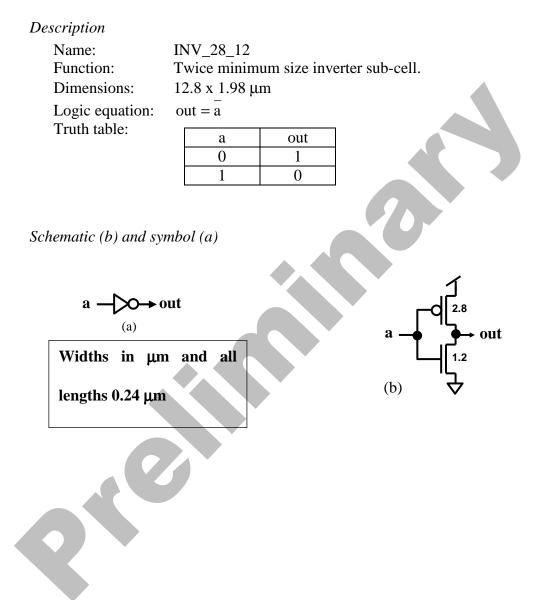

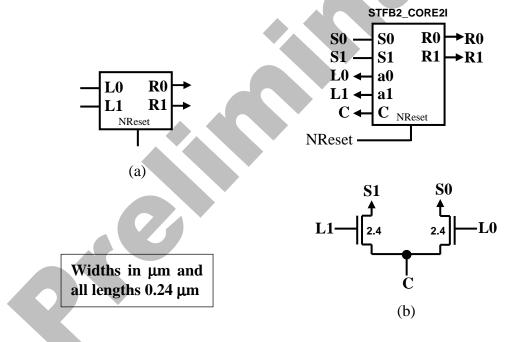

An important characteristic of the STFB architecture is that all the channels are point-to-point channels. This means that there are no forked wires and the channel load is a function of the wire length and the next stage input capacitance. Consequently, since the fanout is always one, the variance on output load is even more dominated by the variation in the wire-lengths than is typical in synchronous designs. Therefore, our initial version of the library introduced here adopts a single-size strategy for each STFB function. The chosen size is reasonable to safely drive, with adequate performance, a buffer load through up to a 1 mm long wire with 0.4 µm width and 0.5 µm spacing. This implies that we can place and route a block as big as 0.5x0.5 mm with essentially no special routing constraints. Larger blocks can also be implemented as long as the wires are constrained to be smaller than this limit. Longer wires would result in poor transition times that could compromise timing assumptions and thus functionality. In the future, special CAD tools to automatically add STFB pipelined buffers within the P&R flow could also accommodate longer connections. Although the TSMC 0.25  $\mu$ m process allows somewhat smaller transistors, we choose, as our minimum NMOS transistor width 0.6  $\mu$ m and minimum PMOS transistor 1.4  $\mu$ m. Also, we assumed, as a basis for the STFB cells creation, that the strength of the main N-stack should be, at least, twice of the minimum size NMOS. This means that the width of each NMOS transistor in the N-stack should be k\*1.2  $\mu$ m, where k is the number of transistors in the path to drive the state to ground. For example: for a 2 transistors path, the width of each N-stack transistor should be at least 2.4  $\mu$ m.

We use, for sizing, a known practical rule that one inverter can drive efficiently four to five times its own input load. By hand calculation we determined that, because the main N-stack has twice the strength of a minimum size inverter, it can safely drive a capacitance load equivalent to 20  $\mu$ m of "gate width", which is sufficient to drive the output transistor and the SCD as shown in Figure 9.

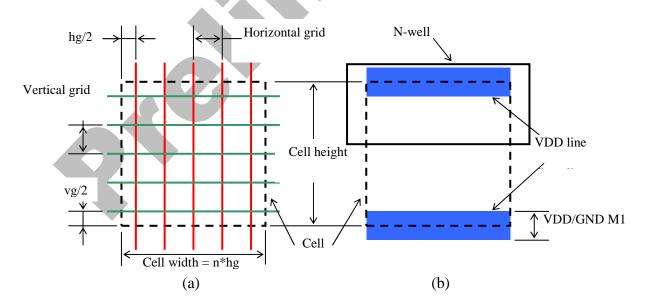

## 4.2 Balanced response

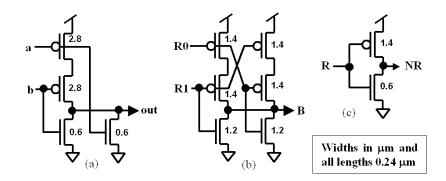

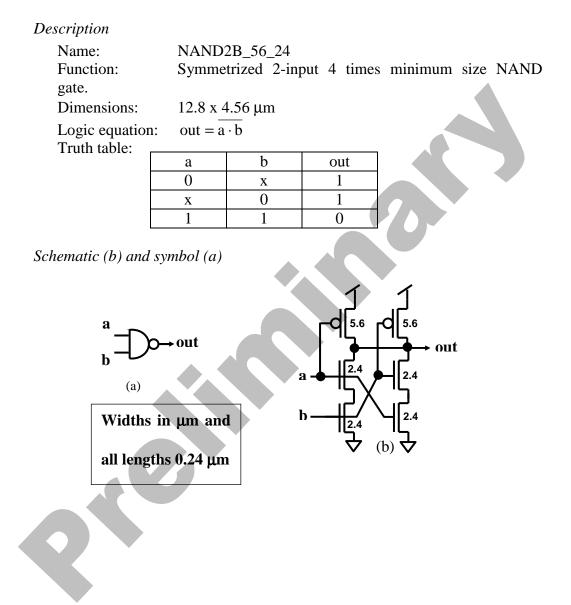

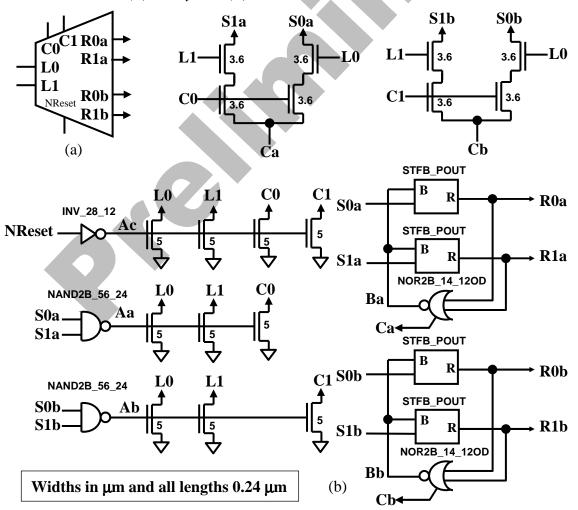

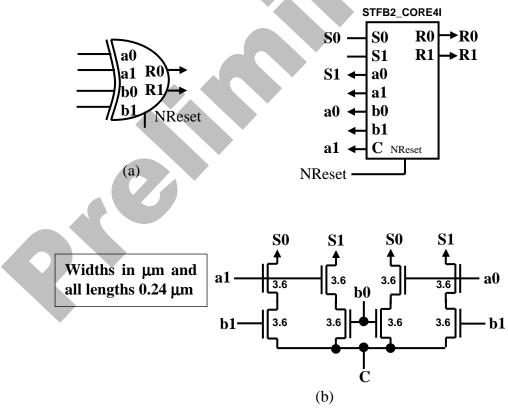

Symmetrized transistor stacks are utilized to perform the SCD and RCD functions inside the cell. Figure 26 shows a 2-input NAND gate where the NMOS transistor stack of the conventional diagram is cut in the middle and symmetrized to allow the same time response for both inputs. This approach minimizes the data influence in the cell timing behavior.

Figure 26. Sub-cell NAND2B\_28\_12: (a) symbol, (b) conventional diagram and (c) implemented balanced input diagram.

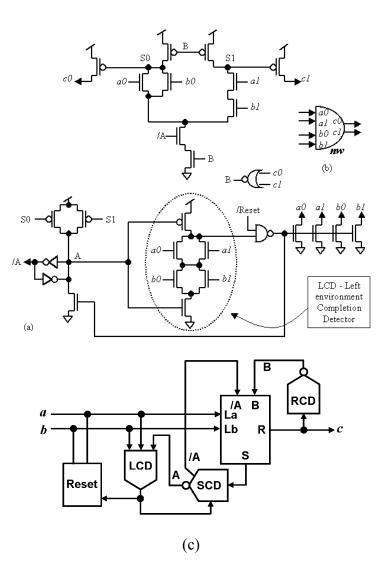

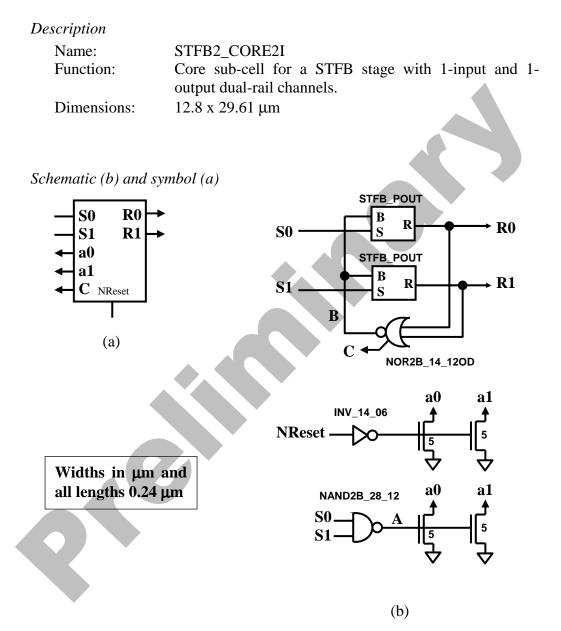

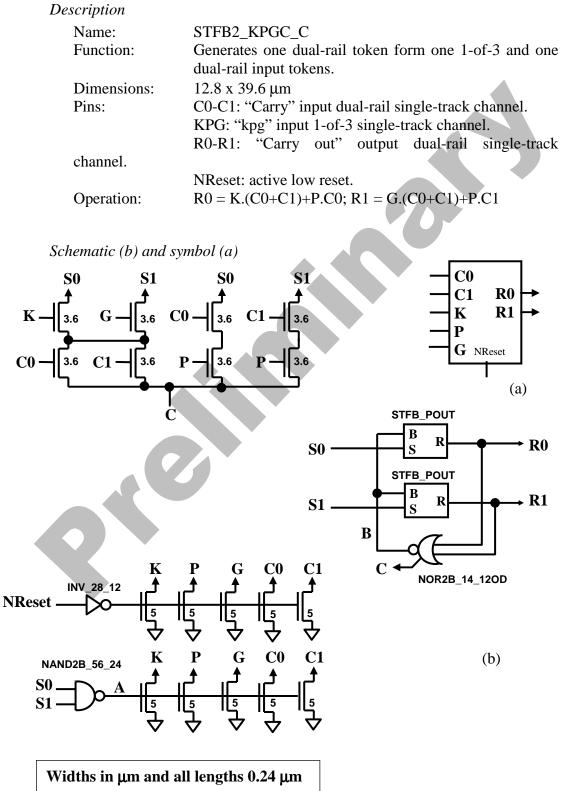

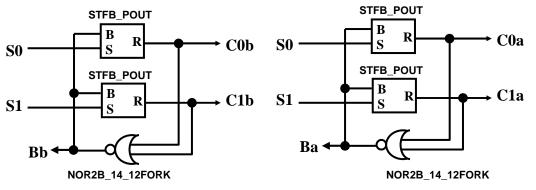

## 4.3 Output sub-cell STFB\_POUT

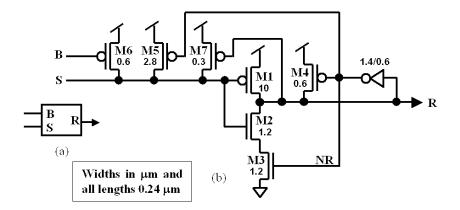

The output driver sub-cell STFB\_POUT is utilized in all STFB cells. It includes the staticizer structure and three PMOS transistors utilized to restore the state input ("S") high as illustrated in Figure 27. If the output channel is empty, the "B" signal is high, "R" is low, and "NR" is high. At the same time, M2 and M3 hold "R" low. When "S" is driven low, the output driver PMOS transistor M1 drives the output "R" high, which makes the minimum size inverter drive "NR" low, deactivating M3 and activating M4 and M5. The RCD (not shown) will also make the "B" signal fall, activating M6. M4 will hold the line high while M5 and M6 drive "S" back high, turning off M1.

M6 and M7 are responsible to fight leakage and charge-sharing. When the output channel is empty, all output rails are low, "B" is high, and thus M7 alone is active. On the other hand, when one output rail is high, "B" is low, and M6 fights leakage and holds "S" high. For this output rail that is high, M6 and M5 are active, while for all other output rails, M6 and M7 transistors are active. M7 can be much smaller than M6 because while "B" is high, the risk of charge-sharing problems is dramatically reduced

as the internal node C at the bottom of the N-stack is actively driven low and thus its capacitance cannot contribute to charge-sharing.

Compared to the original template [18], this template also improves robustness to charge sharing in the N-stack because this output sub-cell now has a lower switching threshold voltage of the "S" signal. In the initial template, M1 was driving the line without M2 and M3, which made the activation threshold of the "S" signal approximately 0.5V (i.e., Vtp) below the power supply voltage ( $V_{DD}$ ). By adding M2 and M3, the activation threshold of "S" is much lower (around 60% of  $V_{DD}$ ).

The introduction of M5 also yields a significant performance improvement allowing longer maximum wire length when compared with the initially proposed template [18]. In particular, M5, controlled by the staticizer inverter ("NR" signal), quickly asserts "S" after its output rail is driven high. This enables M6 to be smaller, thereby reducing the load on the "B" signal enabling a faster cycle-time.

Figure 27. Sub-cell STFB\_POUT (a) block diagram and (b) schematic.

### 4.4 The RCD sizing

The NOR gate in the STFB template (RCD) is also implemented as a symmetrized gate and it is responsible to drive the "B" signal low no later than the signal "NR" goes low in order to disable the N-stack and restore the signal "S", as shown in Figure 28. This is an internal timing constraint that needs to be met to avoid the short-circuit current that would be caused by attempting to restore "S" while the N-stack is still enabled.

Figure 28. B and NR simultaneous activation.

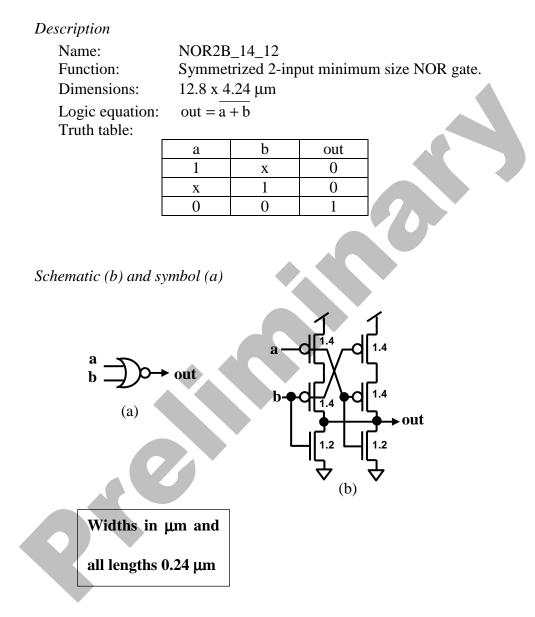

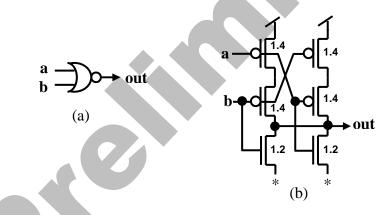

This timing assumption is satisfied by reducing the load connected to the RCD output ( $W_{M6} = 0.6 \mu m$ , which is good enough to fight N-stack charge sharing) and by transistor sizing as shown in Figure 29, where the NMOS transistors of the balanced RCD are 1.2  $\mu m$  wide, while, for a regular minimum sized NOR gate, we would use 0.6  $\mu m$ .

Figure 29. (a) conventional 2-input NOR, (b) balanced RCD and (c) staticizer inverter.

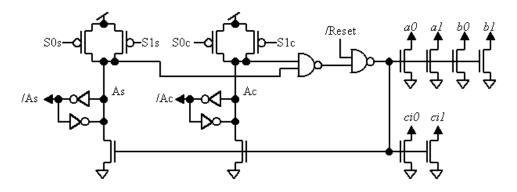

#### 4.5 Input channel reset transistors

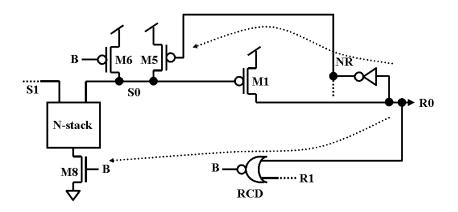

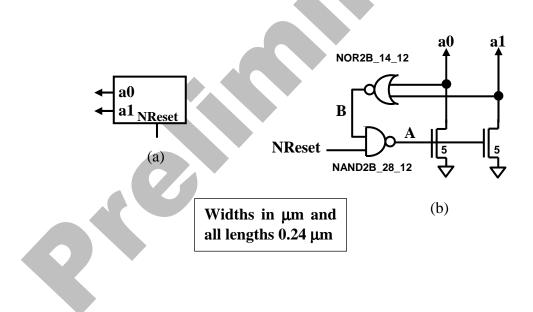

In the STFB template, the input token is consumed by driving the input channel wires low. It is done when the signal "A", generated by the SCD block, activates a set of 5 µm wide NMOS transistors connected to each input wire. Also, to initially reset the entire circuitry, a global "/Reset" (active low reset) signal is used to force all channels low. Initially this signal was simply added as one input to the SCD block [18]. However, a 3-input NAND gate is much less efficient than a 2-input one. Figure 30.a shows the initially proposed 3-input SCD, where a 3-input NAND gate controls the reset transistors. Figure 30.b and c show the implemented reset structure, which uses 2-input NAND gates, allowing a smaller load on the states ("S0", "S1", "S2") and offering a better performance of the SCD for dual-rail and 1-of-3 channels. Notice that the added transistors share the same drain connections, which results in a marginal increase in area and input capacitance for the STFB stage.

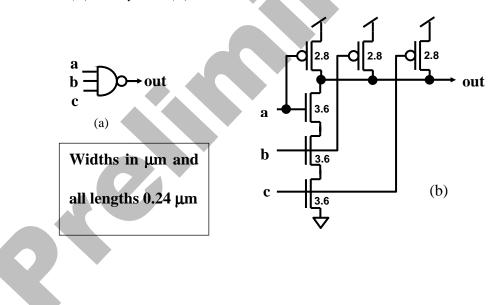

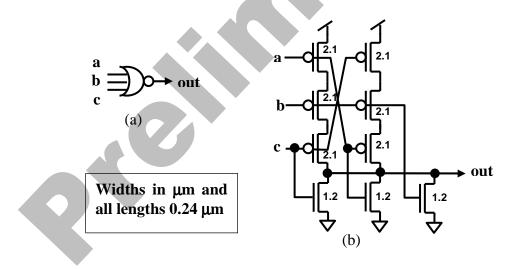

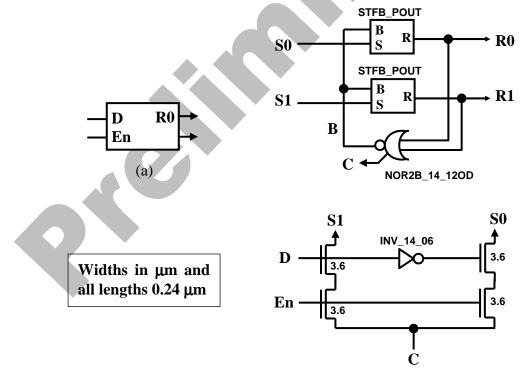

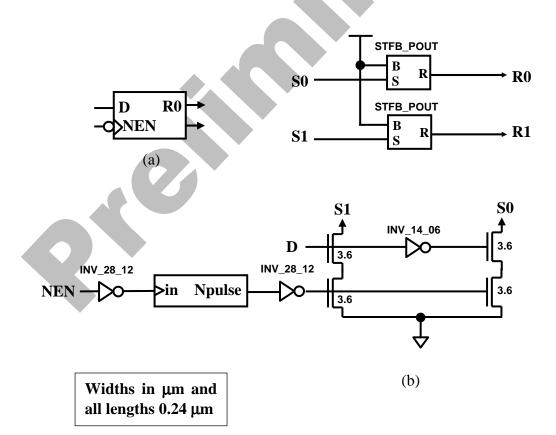

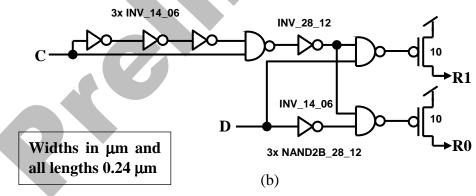

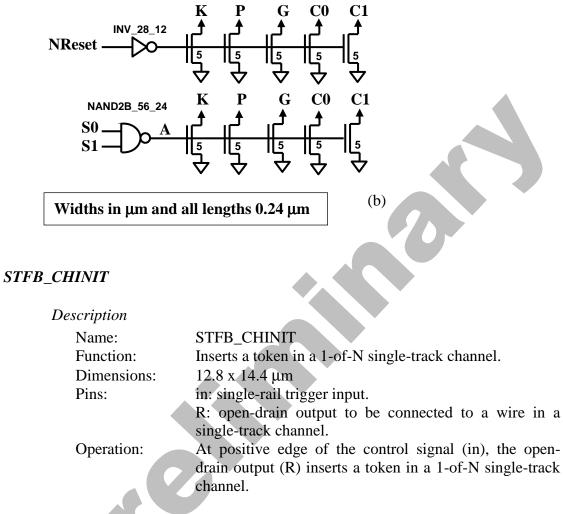

Figure 30. SCD and reset (a) initially proposed and the implemented (b) 1-of-2 and (c) 1-of-3.

## 4.6 Direct-path current analysis

A perceived problem with STFB designs is the amount of direct-path current, also known as short-circuit current, caused by violations of the timing constraint associated with tri-stating a wire before the preceding/succeeding stage drives it. This section analyzes this constraint in detail.

Figure 31 shows a conventional CMOS driver where both the PMOS and the NMOS transistor gates are connected together implementing an inverter. This means that during the rise  $(t_r)$  and fall  $(t_f)$  time of the input voltage  $(V_{in})$  both transistors will be briefly active, allowing a direct-path current from  $V_{DD}$  to ground. Since this current has an approximate triangular shape, we can estimate the direct-path current as  $I_{dp} = I_{peak}/2$  [39].

Figure 31. (a) inverter and (b) direct-path current.

For our STFB pipeline stages, the NMOS transistor gate is connect to signal "A", and the PMOS transistor gate is connected to "Sx" (one of the "states"). Figure 32 shows this implementation and the direct-path current if  $V_A$  happens earlier than  $V_{Sx}$ . If the voltage difference ( $V_{diff} = V_A - V_{Sx}$ ) is zero, the STFB stage  $I_{dp}$  is similar to a conventional inverter. However, if one of the voltage transitions occurs ahead of the other, i.e.,  $V_{diff}$  is different than zero, we may observe a higher peak current during one transition and a smaller peak current during the next transition, or vice-versa.

Figure 32. (a) STFB output/input drivers and (b) direct-path current if  $V_A \neq V_{Sx}$ .

Figure 33 shows the peak direct-path current versus the PMOS-NMOS gate voltage difference during an input rise/fall edge ( $V_{diff} = V_A - V_{Sx}$ ). These values were obtained through DC Hspice simulation analysis using typical parameters with double than our minimum-sized transistors. Notice that, assuming that  $V_A$  and  $V_{Sx}$  have the same shape (both have the same width, rise and fall times), the average peak current is 47

not significantly different than the inverter peak current for  $V_{diff} < 1$  V. This means that a considerable difference between  $V_A$  and  $V_{Sx}$  can be tolerated without a significant jump in power supply consumption.

SPICE simulation also showed that the direct-path current of the STFB templates is no worse than an inverter driving the line, and the timing assumption associated with tri-stating one stage before the other drives the line is not a hard constraint. For our STFB pipeline stages, the time difference between  $V_A$  and  $V_{Sx}$  is bounded by the wire-length constraint to ensure correct operation.

Figure 33. Peak direct-path current versus the PMOS-NMOS gate voltage difference.

Therefore, since we can size the drivers of  $V_A$  and  $V_{Sx}$ , we may avoid most of the  $I_{dp}$  even using our six-transitions STFB template. This careful sizing allows the state signal "Sx" of one stage not to overlap the acknowledge signal "A". This can be illustrated by a simulation of four STFB buffer (U0, U1, U2 and U3), where between U1 and U2 there is a 1 mm long wire and between U0 and U1, and U2 and U3, there is a very short wire as on Figure 34, Figure 35 and Figure 36.

Figure 34 – (a) Two consecutive STFB buffers at full-throughput with 1mm long wire between them and (b) "Sx" (U1) and "A" (U2) signals ( $V_{DD} = 2.5$ V).

Figure 35 – Left side stage "Sx" (U0) and "A" (U1) signals with a very short wire between U0 and U1 ( $V_{DD} = 2.5$ V).

Figure 36 - Right side stage "Sx" (U1) and "A" (U0) signals with a very short wire between U1 and U2 ( $V_{DD} = 2.5$ V).

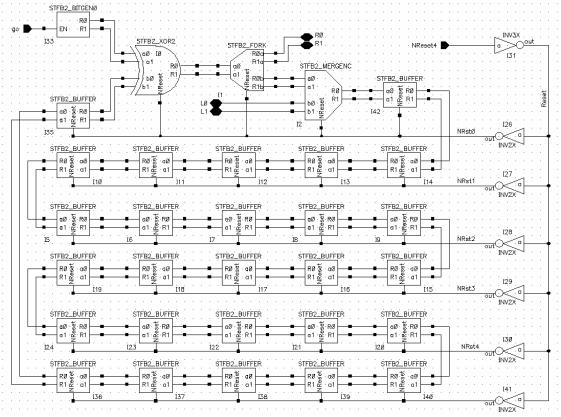

#### 4.7 Reset tree

As the circuits grow in complexity and number of stages, special care needs to be taken with the /Reset signal to avoid the destruction of any token that reaches a stage that is still being reset (reset skew). Also, the /Reset rising edge needs to be fast to guarantee that all the stages connected to that Reset line are operational when the process starts. One option is connect all the stages /Reset wires to a big driver that would reset all stages effectively simultaneously. Another alternative (less brute-force) is to create a balanced reset tree of inverters where, at the leafs of the tree would be connected to all the bit generators, channel initializers, STFB Tx (see Section 3.4.1) and initialized stages and passive stages would be connected to leafs that have two or more fewer inverters from the root. This allows the passive stages to come out of reset at least two or more transitions earlier than their active counterparts, providing a reset margin ensuring the passive stages are ready to accept tokens from their active counterparts.

#### 4.8 Noise margin

As for any family of digital circuits, we need to consider the STFB templates reliability to noise. We use the worst-case analytical analysis described in [12], and applied in [58] and [15], with the intended process (TSMC 0.25 $\mu$ m) parameters, where the minimum transistor size used in our circuits are:  $Wn = 0.6 \mu$ m and  $Wp = 1.4 \mu$ m for the minimum width of the NMOS and PMOS transistors respectively. For this analysis, we are using the transistor sizing strategy described on Section 4.1.

Figure 27 shows the STFB output stage where the state signal "S" is hold high by the transistor M7. This means that the NMOS transistor stack has to over-power the state pull-up transistors M7 in order to lower the respective state "S". Therefore, a high level input signal ( $V_{IH}$ ) needs to be higher than 0.75V, which is bigger than just the NMOS threshold voltage ( $V_{In} = 0.53$ V). If M7 were stronger,  $V_{IH}$  would be higher (close to half of the power supply voltage:  $V_{DD} / 2$ ). However, this would also slow down the circuit and increase the direct-path current for every operation.

Noise can cause a signal  $V_S$ , the ideal correct input value, to be perceived by the receiver circuit as  $V_R = V_S + V_N$ , where  $V_N$  is additive noise. If  $V_S = 0$  V, the worst-case noise must be smaller than  $V_{IH}$  (0.75V). For  $V_S = V_{DD}$ , the worst case noise must be smaller than half  $V_{DD}$  to avoid change the "state" of the staticizer holding the line. To be reliable we need to have a signal-to-noise ratio (*SNR*) bigger than one for both cases as shown in equations (1) and (2).

$$SNR_L = \frac{V_{IH}}{V_N} \tag{1}$$

51

$$SNR_{H} = \frac{1}{2} \cdot \frac{V_{DD}}{V_{N}}$$

(2)

A good part of the system-created noise is proportional to the signal amplitude swing, which means that increasing  $V_{DD}$  will not improve the *SNR*. Therefore, we will analyze the noise as shown in equation (3).

$$V_N = K_N V_{DD} + V_{NI} \tag{3}$$

where,  $K_N V_{DD}$  represents the noise sources that are proportional to  $V_{DD}$  (2.5V) such as cross talk and signal-induced power supply noise, and  $V_{NI}$  represents the noise sources that are independent of the signal amplitude such as receiver offsets and unrelated power supply noise.

| Parameter                | Definition                                                                                          | Value   |

|--------------------------|-----------------------------------------------------------------------------------------------------|---------|

| K <sub>C</sub>           | Cross talk coupling coefficient for two 100 μm long 0.4<br>μm wide metal 4 wire with 0.5 μm spacing | 0.1     |

| <i>Attn<sub>CP</sub></i> | PMOS staticizer cross talk noise attenuation.                                                       | 0.97    |

| Attn <sub>CN</sub>       | NMOS staticizer cross talk noise attenuation.                                                       | 0.88    |

| $K_{PS}$                 | Power supply noise due to signal switching.                                                         | 5% [58] |

| $K_{NP}$                 | <i>Worst case:</i> $K_{NP} = Attn_{CP}.K_C + K_{PS}$                                                | 0.147   |

| $K_{NN}$                 | <i>Worst case:</i> $K_{NN} = Attn_{CN}K_C + K_{PS}$                                                 | 0.138   |

| Rx_O                     | Next stage input offset                                                                             | 0.1 V   |

| Rx_S                     | Next stage sensitivity                                                                              | 0       |

| PS                       | Power supply noise (5% [58] of 2.5V)                                                                | 0.125 V |

| <i>Attn<sub>PS</sub></i> | Power supply noise attenuation                                                                      | 1       |

| Tx_O                     | Output offset                                                                                       | 0       |

| $V_{NI}$                 | Worst case: $V_{NI} = Rx_O + Rx_S + Attn_{PS}PS + Tx_O$                                             | 0.23 V  |

| $V_{NP}$                 | Worst case noise: $V_{NP} = K_{NP}.V_{DD} + V_{NI}$                                                 | 0.60 V  |

| V <sub>NN</sub>          | Worst case noise: $V_{NN} = K_{NN}.V_{DD} + V_{NI}$                                                 | 0.58 V  |

| SNR <sub>H</sub>         | Worst case $SNR_H = 1.25 / V_{NN}$                                                                  | 2.2     |

| SNR <sub>L</sub>         | Worst case $SNR_L = 0.75 / V_{NP}$                                                                  | 1.3     |

Table 1 - Noise source analysis

Table 1, shows the parameters used in our analysis. The meaning of each parameter is detailed below:

$K_C$ : The cross talk coupling coefficient  $K_C$  is estimated by the equation below:

$$K_C = \frac{C_C}{C_O + C_C} \tag{4}$$

where,  $C_C$  is the parasitic coupling capacitance between the "aggressor" and the "victim" wires, and  $C_O$  is the capacitance between the "victim" wire and the substrate including the input and output capacitance of the stages connected by this wire. For a 100 µm long, with spacing of 0.5 µm, and 0.4 µm wide wire implemented using metal 4 with in the TSMC 0.25 µm process, and connecting the output of an STFB buffer to an input of another STFB buffer, we have, approximately, the wire to substrate capacitance  $C_W = 2.5$  fF, the STFB buffer output capacitance (including staticizer)  $C_{out}$ = 37.7 fF, and the STFB buffer input capacitance  $C_{in} = 17.4$  fF. Therefore, we estimate:  $C_O = C_W + C_{in} + C_{out} = 2.5 + 37.7 + 17.4 = 57.6$  fF. Since the capacitance between two metal 2 wires, for a wire spacing of 0.5 µm, is  $6.45 \times 10^{-2}$  fF/µm, we estimate  $C_C = 6.45$  fF, resulting  $K_C = 0.1$ .

*Attn<sub>C</sub>*: The static driver cross talk noise attenuation  $Attn_C$  should be near half if the line were continuously driven. However, STFB stages actively drive the line high during 3 transitions, and low during 3 transitions. This means that, unless the pipeline is running at full throughput (6 transitions per token), the output staticizers are holding the line when it is not being actively driven. To compute a worst-case scenario, we considered the victim line hold by the staticizer, while the aggressor is actively driven. 54

We can compute  $Attn_{CN} = \text{Rsn}/(\text{Rsn} + \text{Rdp})$  and  $Attn_{CP} = \text{Rsp}/(\text{Rsp} + \text{Rdn})$ , where Rs is the staticizer impedance and Rd is the driver impedance. For the STFB buffer we have  $\text{Rsn} = 6.9 \ \Omega$ ,  $\text{Rdn} = 0.82 \ \Omega$ ,  $\text{Rsp} = 24.2 \ \Omega$  and  $\text{Rdp} = 0.94 \ \Omega$ , resulting  $Attn_{CN} = 0.88$ and  $Attn_{CP} = 0.97$ , which means almost no attenuation. In other words, the current staticizers are very weak and make little difference with respect to the noise.

$K_{PS}$ : The power supply noise due to signal switching  $K_{PS}$  is assumed to be 5% as in [58].

$Rx_O$ : The next stage input offset  $Rx_O$  is the difference between the nominal  $V_{IH}$ and the minimum  $V_{IH}$  expected (reducing  $V_{IH}$  reduces our noise margin), estimated to be < 0.1V.

$Rx\_S$ : The next stage sensitivity  $Rx\_S$  represents the extra voltage range required over  $V_{IH}$  in order to properly activate the next stage. This, in fact, would improve our noise margin since it would require a final  $V_{IH}$  closer to  $V_{DD}/2$ . Also, in our STFB stage, once the driven state (S0 or S1) is low enough to activate the PMOS driver, the stack pull-up became weaker and the switching point is very abrupt due to the positive feedback. Therefore we selected 0V, meaning that the stage will react immediately once  $V_{IH}$  is reached.

*PS*: The power supply noise unrelated to signal switching *PS* is assumed to be 5% as in [58].

*Attn*<sub>PS</sub>: The power supply noise attenuation  $Attn_{PS}$  is 1, meaning: no attenuation (worst-case) assuming  $V_{IH}$  is independent of the power supply.

$Tx_O$ : The output sensitivity  $Tx_O$  represents variation in the output voltage, which is 0V for full-swing (rail-to-rail) circuits.

The final  $SNR_L$  is 1.3 for the two 100 µm parallel lines. For 300 µm lines, the  $SNR_L$  would be approximately equal to one, the safe limit for the worst-case SNR. Although this analysis is very conservative, based on it, we dedicated extra care in the layout and post-layout verification to avoid malfunctions due to noise issues.

However, this analysis is limited to  $0.25 \ \mu m$  or bigger technologies since it does not take into account the line resistance effect, which is very important for deep submicron processes. For these processes, a more robust single track protocol is needed, and we propose the static single-track (SST) protocol as described below.

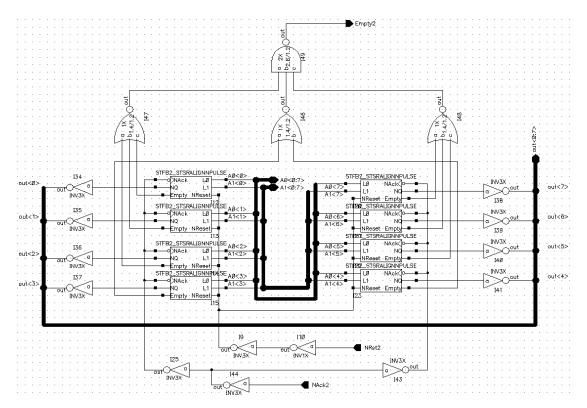

#### 4.9 Static single-track protocol

For deeper sub-micron technologies, the impact of increased wire resistance must be addressed. In particular, dynamic long-distance wires are very dangerous because staticizers are generally too weak to combat coupling noise in the presence of highly resistive wires. Naive solutions include shielding the at-risk wires, increasing the size of staticizers, and/or increased the spacing between wires, all of which have substantial costs in area, power, and/or performance. This section introduces a novel Static Single-Track (SST) protocol that addresses these issues by continuously driving the wire at only a marginal cost in area, power, and performance.

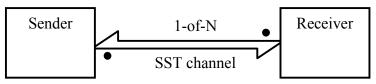

Figure 37. 1-of-N Static Single-Track asynchronous channel.