## LIBRARY CHARACTERIZATION AND STATIC TIMING ANALYSIS

#### OF ASYNCHRONOUS CIRCUITS

by

Mallika Prakash

#### A Thesis Presented to the FACULTY OF THE USC VITERBI SCHOOL OF ENGINEERING UNIVERISTY OF SOUTHERN CALIFORNIA In Partial Fulfillment of the Requirements for the Degree MASTER OF SCIENCE (COMPUTER ENGINEERING)

December 2007

Copyright 2007

Mallika Prakash

# Acknowledgements

I thank my advisor, Prof. Peter Beerel who has been the driving force behind this thesis for being an excellent teacher, mentor and friend, and his wife Janet and baby girl Kira for providing a welcoming and friendly environment to work in. I thank the entire Asynchronous CAD/VLSI Group at USC, Georgios Dimou, Pankaj Golani, Arash Saifhashemi, Roger Su, Gokul Govindu, Amit Bandlish and Prasad Joshi for their support and companionship during the long hours that went into this work and for very useful brainstorming Friday group meetings. Special mention goes to Pankaj, Amit, Prasad and Rahul Rithe (from Indian Institute of Technology, Kharagpur) for their help with characterizing SSTFB cells and debugging the characterization flow and Gokul and Amit for writing and maintaining the TCL script to convert HSpice measure files to the liberty format.

I also thank Fulcrum Microsystems for the use of PCHB and MLD libraries, Andrew Lines especially for his critical feedback on the STA flow, Professor Ken Stevens of University of Utah for his help in formally verifying the PCHB relative timing constraints, Giorgios Dimou for providing the PCHB and MLD test cases for the static timing analysis flow, Marly Roncken at Intel for her technical advice, Silistix UK Ltd. for giving me the opportunity to develop a static timing analysis flow for their asynchronous design methodology as a summer 2007 intern, and my manager and mentor David Jackson and John Bainbridge at Silistix for guiding me towards a successful internship. This work was in part supported by an SRC Grant CADTS-1425 and by Viterbi School of Engineering Teaching Assistantships. I thank the entire EE-Systems staff, Diane Demetras, Rosine Sarafian, Mandy Sheedy and Annie Yu for entertaining endless questions with patience.

I am grateful to my thesis committee members Prof. Massoud Pedram and Prof. Melvin Breuer for their valuable feedback and my professors at Illinois Institute of Technology, Prof. James Stine, Prof. Donald Ucci and Prof. Jaffar Saniie for cultivating my passion for research and building my technical foundation.

My parents Sunil and Anju and my siblings Soumya and Suryanshu have always supported me and believed in me and I thank them for their unconditional love, faith and advice that can not be matched. My fiancé Gokul has been my greatest inspiration to excel in whatever I do and his unreserved love, trust and confidence in me are unsurpassed.

# Table of Contents

| Acknowledgements                                                                                                                                                                                                                                                                       | ii                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| List of Figures                                                                                                                                                                                                                                                                        | vi                                     |

| List of Tables                                                                                                                                                                                                                                                                         | viii                                   |

| Abstract                                                                                                                                                                                                                                                                               | ix                                     |

| Chapter 1                                                                                                                                                                                                                                                                              | 2                                      |

| 1. Introduction                                                                                                                                                                                                                                                                        | 2                                      |

| Chapter 2                                                                                                                                                                                                                                                                              | 6                                      |

| 2. Background                                                                                                                                                                                                                                                                          | 6                                      |

| <ul><li>2.1. Delay and Power Characterization</li><li>2.2. Static Single Track Full Buffers</li><li>2.3. Pre-Charged Half Buffers</li><li>2.4. Multi-Level Domino</li><li>2.5. Hierarchical design style</li></ul>                                                                     | 6<br>7<br>9<br>11<br>13                |

| Chapter 3                                                                                                                                                                                                                                                                              | 15                                     |

| 3. Library Characterization for SSTFB                                                                                                                                                                                                                                                  | 15                                     |

| <ul> <li>3.1. Defining Timing Arcs</li> <li>3.2. Creating a Simulation Environment</li> <li>3.2.1. Input waveforms</li> <li>3.2.2. Input Slew and Load Capacitances</li> <li>3.3. Measuring power</li> <li>3.4. Measuring Pin Capacitances</li> <li>3.5. Library Generation</li> </ul> | 15<br>16<br>16<br>17<br>18<br>20<br>23 |

| 3.6. V      | /alidation Results                                                             | 24 |

|-------------|--------------------------------------------------------------------------------|----|

| <u>Char</u> | oter 4                                                                         | 28 |

| 4. St       | atic Timing Analysis for Asynchronous Circuits                                 | 28 |

| 4.1. N      | Modeling relative timing constraints                                           | 28 |

|             | Non-sequential data checks                                                     | 28 |

|             | Associated challenges                                                          | 30 |

|             | Modeling the minimum pulse width constraints                                   | 34 |

|             | Breaking timing loops                                                          | 35 |

|             | Loop breaks for template-based designs                                         | 37 |

|             | Loop breaks for hierarchical design style based circuits                       | 37 |

|             | Fully automated scripts                                                        | 38 |

|             | Adeling performance                                                            | 39 |

| 4.5. K      | Results                                                                        | 40 |

| <u>Char</u> | oter 5                                                                         | 44 |

| 5. Co       | onclusions and Future Work                                                     | 44 |

| Bibli       | iography                                                                       | 46 |

| Арре        | endix A                                                                        | 48 |

| A.1.        | Relative timing constraints verification script for PCHB                       | 48 |

| A.2.        | Performance verification script for PCHB                                       | 53 |

| A.3.        | Relative timing constraints verification script for MLD                        | 59 |

| A.4.        | Performance verification script for MLD                                        | 62 |

| A.5.        | Relative timing constraint verification for hierarchical design based circuits | 68 |

# List of Figures

| Figure 2-1: | General structure of a static single track full buffer and its timing diagram                                                                                            | 7  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2-2: | Static STFB dual-rail buffer                                                                                                                                             | 8  |

| Figure 2-3  | Block diagram for the PCHB template                                                                                                                                      | 10 |

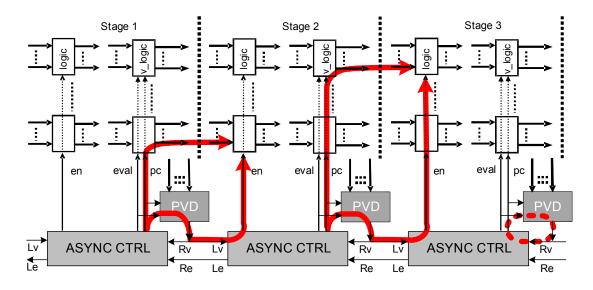

| Figure 2-4  | Three stage PCHB pipeline highlighting the relative timing constraint and the timing loops                                                                               | 11 |

| Figure 2-5: | Block diagram of a multi-level domino pipeline highlighting the relative timing constraint (thick red lines) and the minimum pulse width constraints (dotted red lines). | 12 |

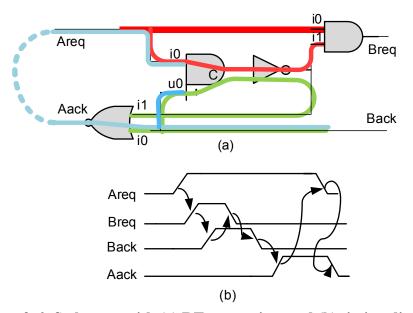

| Figure 2-6  | S-element with (a) RT constraints and (b) timing diagram                                                                                                                 | 13 |

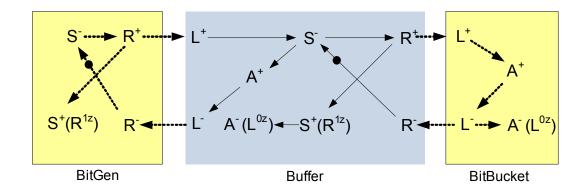

| Figure 3-1: | Abstract marked graph of a SSTFB buffer surrounded by a bit generator and generator                                                                                      | 16 |

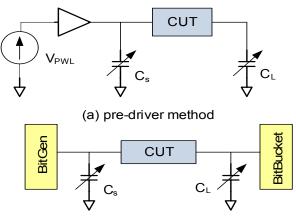

| Figure 3-2: | Test setup for (a) synchronous circuits (b) asynchronous circuits                                                                                                        | 17 |

| Figure 3-3: | Addition of a 0V source to measure the internal energy associated with the timing arcs S0 <sup>-</sup> $\rightarrow$ A <sup>+</sup>                                      | 19 |

| Figure 3-4: | Measuring pin capacitance of pin A0 of a buffer                                                                                                                          | 21 |

| Figure 3-5: | Measuring pin capacitance of pin R0 of a buffer                                                                                                                          | 21 |

| Figure 3-6  | SSTFB BitBucket schematic (a) incorrect HSpice set-up                                                                                                                    | 23 |

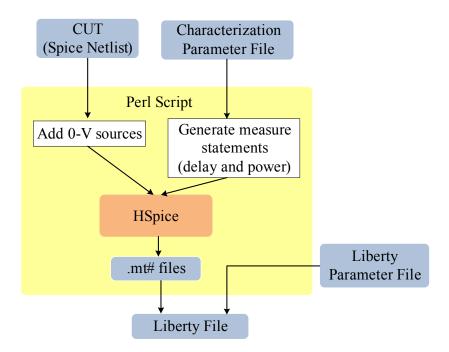

| Figure 3-7: | Characterization flow                                                                                                                                                    | 24 |

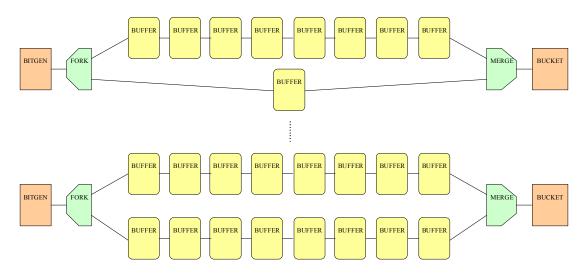

| Figure 3-8: | Unbalanced non-linear pipelines used for validating the characterization flow.                                                                                           | 25 |

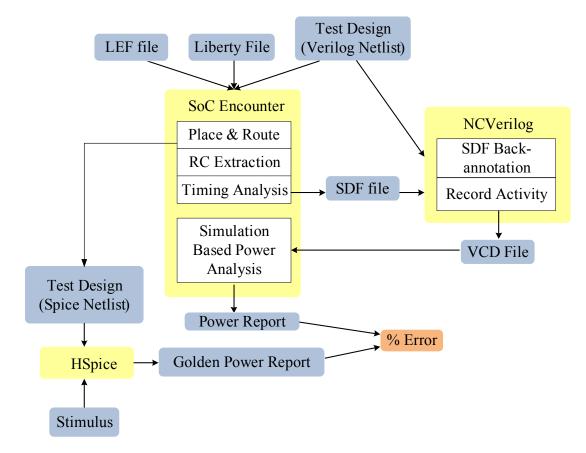

| Figure 3-9: | Validation flow                                                                                                                                                          | 25 |

| Figure 3-1  | D: Fork-join pipeline experiment – performance                                                                                                                           | 27 |

| Figure 3-1  | 1: Fork-join pipeline experiment - power                                                                                                                                 | 27 |

| Figure 4-1: | Non-sequential data to data check                                                                                                                                        | 29 |

| Figure 4-2: | Modeling the relative timing constraints using set_data_check for (a) PCHB template (b) MLD template (c) S-element                                                       | 30 |

| Figure 4-3  | Configuration of three S-elements creating overlapping constraints                                                                                                       | 32 |

| Figure 4-4: | Modified set_data_check commands for (a) PCHB template (b) MLD template and (c) S-element                                                                                | 33 |

vi

| Figure 4-5: Multiple fake related pins per constraint                                           | 34 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 4-6: Modeling minimum pulse width constraint                                             | 35 |

| Figure 4-7: Static loop breaking                                                                | 36 |

| Figure 4-8: Clocks and loop breaks for (a) PCHB and (b) MLD templates                           | 37 |

| Figure 4-9: Relative timing constraints verification script for PCHB                            | 39 |

| Figure 4-10: Relative timing constraints verification report for (a) PCHB and (b) MLD templates | 42 |

| Figure 4-11: Performance verification report for (a) PCHB and (b) MLD templates                 | 43 |

# List of Tables

| Table 1: Run times for RT constraints verification | 41 |

|----------------------------------------------------|----|

| Table 2: Run times for performance verification    | 41 |

# Abstract

For main stream acceptance of asynchronous circuits, a mature EDA tool flow is necessary that leverages off commercially available libraries and tools for synchronous circuits. Many asynchronous templates however rely on specialized and complex circuits that are not present in commercial libraries. For such templates, designers either technology map these cells to existing libraries at the cost of area and performance or rely on full-custom design and extensive SPICE simulation to verity timing correctness and performance. This thesis addresses both of these issues by developing both library characterization and static timing analysis flows for nonstandard asynchronous circuit templates that together support back-annotated power and timing simulations as well as static timing and performance verification. We first create a fully-automated characterization flow for the static single-track full-buffers template. We then develop a fully-automated static-timing flow for timing and performance verification using the gold-standard commercial tool, Synopsys PrimeTime. The proposed flow is successfully demonstrated on three different asynchronous design styles.

Chapter 1

# **1. Introduction**

Asynchronous design has begun to demonstrate its advantages in the commercial marketplace. There is a growing need for high performance low power circuits in areas such as on-chip interconnect and globally asynchronous locally synchronous (GALS) systems. Many asynchronous circuits fulfill these needs but are not easily accepted by designers due to a lack of support by commercial CAD tools. Asynchronous logic cells not found in standard-cell libraries, such as dual-rail domino logic and dynamic C-elements with staticizers, must be characterized for both timing and power so as to not limit the designers to full-custom design and time consuming SPICE simulations to verify timing and correctness. Library characterization for such non-standard cells enables back annotated Verilog simulations, timing driven place and route and is a pre-cursor to timing sign-off with commercial static analysis tools.

In general, the challenges of characterizing asynchronous cells comes from their more general circuit structure that may include internal combinational loops, bidirectional pins, and mutual exclusion rules on dual-rail or 1-of-N inputs. These input constraints and general structures do not conform to the standard latch or flip-flop templates supported by commercial library characterization tools. Consequently, library characterization has been a limiting factor for otherwise promising asynchronous design styles. In particular, the library characterization challenges are epitomized in the proposed next generation STFB circuit family called static singletrack full buffers (SSTFB) [5][6][7]. In [4] layout and abstract views of STFB were developed and used to design a tree adder test chip. This library was extended in [8] to include timing characterization which enabled back-annotated timing analysis, but extensions to SSTFB and verifying power consumption was left as future work. SSTFB was used in [6] to implement a turbo decoder but due to the absence of characterized delay information, the authors were limited to time consuming postlayout simulations in Nanosim. Using a characterized library, timing correctness and performance can be analyzed either through back-annotated simulations or static analysis.

Similarly, the timing constraints necessary for correctness in an asynchronous circuit can be much more complex than setup and hold constraints on flip-flops and latches. In this thesis we adopt the relative timing (RT) approach introduced in [16] for modeling timing constraints necessary for correct operation. Relative timing is premised on the observation that timing correctness typically depends on enforcing a relative ordering between signals that can and should be explicitly identified and verified. Coupled with absolute margins, such RT constraints should be adhered to during synthesis and P&R and then verified post-layout. Previous work in RT such as in [3][13][17][18] present various approaches for using the relative timing approach during synthesis and verification of asynchronous systems. However, the connection between relative timing and post-layout sign-off using static timing analysis has yet to be addressed.

The first half of this thesis addresses the characterization challenges by demonstrating an effective timing and power characterization flow for static STFB cells. It describes the decomposition of SSTFB cell behavior into a set of timing arcs that can be understood by commercial place and route and back annotation tools. It then describes a novel methodology and tool kit to automatically characterize the library and represent the information in the commercially supported Liberty file format. The second half of this thesis focuses on how both relative-timing constraints as well as performance (e.g., throughput) targets can be verified using standard STA tools for three different asynchronous design methodologies. The first is the well-used pre-charged-half-buffer template [10][12], the second is a novel template in which stages consist of multi-level domino-dual-rail logic and a full-buffer handshake controller and the third is a non template-based hierarchical design methodology. We develop fully-automated scripts that verify all relative timing assumptions (e.g., isochronic forks) as well as the gate-level performance of any circuit designed with these templates.

Related work includes the application of STA tools in desynchronization briefly described in [1][3]. The authors describe a fully-automated flow from synthesis to place and route in which an asynchronous design is produced from a synchronous Verilog netlist by replacing each flip-flop with two latches and the clock with handshaking control signals coupled with run-time-configurable matched delay lines. As part of their flow, STA is used to verify correct timing in the specific semidecoupled four-phase controllers used but extensions to the template-based styles covered in this thesis are not addressed. In addition, the verification is not based on relative timing but rather on max-delay constraints with absolute metrics, which can lead to false negatives. Virtual clocks are added to the design to model the datapath as a conventional master-slave latch-based design with non-overlapping clocks. This guarantees that the latency of the combinational logic is constrained and that the associated delay-lines will be sufficiently long. In addition, the authors do not address how STA could verify the performance of the desynchronized circuit and instead rely on time-consuming back-annotated simulation.

We also note that STA has been integrated into the single-rail back-end design flow developed by Handshake Solutions, but to the best of our knowledge these details are not published and thus a comparison to our approach is not possible.

# Chapter 2

# 2. Background

This chapter presents background material on delay and power characterization, followed by some example circuit families that are used in the characterization and static timing analysis flows.

# 2.1. Delay and Power Characterization

Both delay and power consumption of a library are characterized and stored in an industry format (Liberty) file. For delay, both pin to pin delays and the corresponding output slopes are typically characterized for identified timing arcs as a function of load and/or input slope. In general, this allows slews to propagate during delay and timing analysis and be used to characterize and analyze power consumption.

For power, both static and dynamic sources of power are characterized. Dynamic power is made up of internal power and switching power. The former is dissipated by the cell in the absence of a load capacitance and the latter is the component that is dissipated while charging/discharging a load capacitance. Dynamic power is measured per timing arc (as with delay). Static dissipation is due to leakage currents through 'OFF' transistors and can be significant when the circuit is in the idle state (there is no switching activity). It has four principle sources: reverse-biased junction leakage current, gate induced drain leakage, gate direct-tunneling leakage and subthreshold (weak inversion) leakage. For 180nm, gate leakage is about 0.1% of total static power and subthreshold leakage dominates. The other two components are much smaller and thus generally ignored. With the above simplification, leakage power can be computed as the product of supply voltage and the sub-threshold leakage current. Unlike delay and dynamic power, leakage power is typically represented as a single value per cell.

# 2.2. Static Single Track Full Buffers

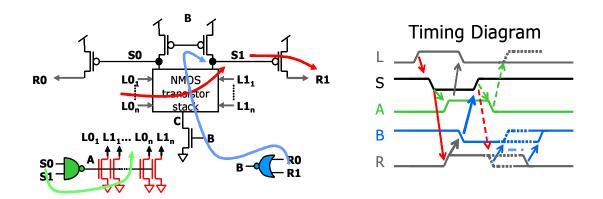

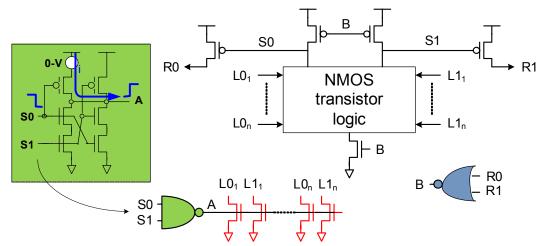

Static single track full buffer (SSTFB) is an asynchronous design template that uses dual rail domino pre-charged by an asynchronous control signal instead of a clock. It uses a 2-phase handshaking protocol where the sender pulls the channel high and the receiver pulls the channel low. Figure 2-1 shows the general structure of a static single track full buffer.

Figure 2-1: General structure of a static single track full buffer and its timing diagram

When there is no token on the right channel (R) (R is low meaning the channel is empty), the right environment enables the domino logic to process a new token. When a new token arrives at the left channel (L goes high) it is processed by lowering the state signal "S", which creates an output token on the right channel (R goes high) and asserts "A" removing the token from the left channel via reset NMOS transistors. The presence of the output token on the right channel restores the state signal and deactivates the NMOS transistor at the bottom of the N-stack thus disabling the stage from firing while the output channel is busy. The NAND gate is commonly called the state completion detector (SCD) and the NOR gate is called the right completion detector (RCD). A more detailed schematic of a SSTFB buffer is shown in Figure 2-2.

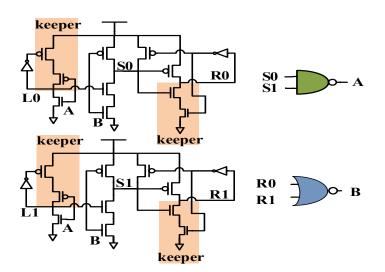

Figure 2-2: Static STFB dual-rail buffer

Notice that after the sender drives the line high, the receiver is responsible for actively keeping the line high (via the input keepers) until it wants to drive it low. Similarly, after the receiver drives the line low, the sender is responsible for actively keeping the line low until it wants to drive it high (via the output keepers). The line is

always statically driven and no fight with staticizers exists. This hand-off technique enables the hold circuitry to be sized to a suitable strength creating a tradeoff between performance/power/area and robustness to noise. The inverters in the hold circuitry can be also be skewed such that they turn on early creating an overlap between the driving and hold logic. This overlap avoids the channel wire being in a tri-state condition thus making the circuit family more robust to noise. The overlap also helps ensure that the channel wires are always driven close to the power supplies further increasing noise margins.

The local cycle time of the static STFB template is 6 transitions with a forward latency of 2 transitions. It is called a full-buffer because each buffer stage can hold one token. The template is very flexible and can be expanded to implement different functionalities by enabling multiple 1ofN input channels, arbitrary NMOS pull down logic and multiple 1ofN output channels [5][6][7].

#### 2.3. Pre-Charged Half Buffers

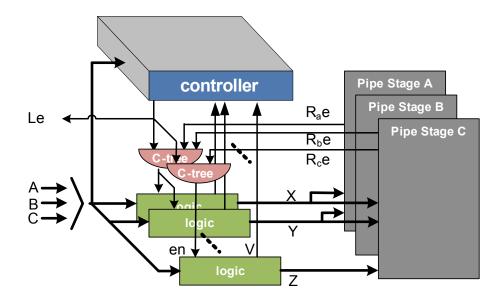

Pre-Charged Half Buffer (PCHB) is a QDI template developed at Caltech [9][10]. A single PCHB stage uses dual rail domino logic pre-charged by a single asynchronous control signal 'en' instead of two signals 'en' and 'pc' as in [10][11]. The domino block produces a dual rail output channel R and a control signal V which is used to detect its validity. Figure 2-3 shows a basic block diagram of PCHB. In general, a pipeline stage can contain multiple logic blocks to support multiple inputs or multiple outputs. Each logic block detects the validity of its outputs and produces a

signal V. The control block detects the validity of the inputs and combines it with the V signals from all the logic blocks to generate the acknowledgement Le. The acknowledgement signals from the next stages are combined using a tree of c-elements and then combined with Le out of the controller to generate en for the logic block.

Figure 2-3: Block diagram for the PCHB template

The circuit relies on a relative timing constraint (shown by the thick green lines in Figure 2-4) for correct operation. In words, the input to the domino block should go low (neutral) before a rising transition on the control signal 'en' occurs. If this relative timing constraint is violated, the domino block may evaluate with old data creating an extra token on the output channel. Note that there are similar relative timing constraints associated with all the rails. These timing assumptions are a relaxed interpretation of the underlying isochronic fork assumption at the data inputs of this template and were verified to be sufficient for correctness by Ken Stevens using his tool RT-Analyze [15]. This template also has several timing loops (dotted lines) spanning a single to multiple stages which together dictate throughput.

Figure 2-4: Three stage PCHB pipeline highlighting the relative timing constraint and the timing loops

#### 2.4. Multi-Level Domino

MLD also uses dual rail domino to implement the logic blocks and a separate control block like in PCHB. A pipeline stage can contain n levels of domino blocks, n-l levels of which are pre-charged and evaluated by a single control signal 'en' while the  $n^{th}$  level of domino is pre-charged and enabled by different control signals 'pc' and 'eval' respectively as shown in Figure 2-5. The important feature of this template is that the last level of domino per pipeline stage does not pre-charge until the next pipeline stage has consumed the token. This makes the template fast as the first n-l domino blocks can start evaluating early with new data without having to wait for the next stage to consume the previous data. The last level of domino per stage is a special logic cell that generates a valid signal and is referred to as a v\_logic cell. The pre-charge validity detector (PVD) as the name suggests is pre-charged low by the controller and only detects the validity of the stage by combining the valid signals

from all the v\_logic domino cells in that stage. The v\_logic cells and the PVD are precharged simultaneously. It is important to note here that the neutrality of the data rails is not checked explicitly. This results in a relative timing constraint on the precharge delay and minimum pulse width constraints on 'en' and 'pc'. In particular, the data inputs to the domino logic block should go neutral before the 'en' to the domino block goes high. This is to prevent the domino block from re-evaluating with old data. The minimum pulse width constraints are that the pre-charge signals 'en' and 'pc' should be low for a sufficiently long amount of time so as to pre-charge the domino blocks completely.

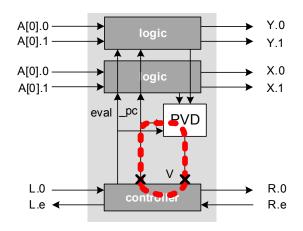

Figure 2-5: Block diagram of a multi-level domino pipeline highlighting the relative timing constraint (thick red lines) and the minimum pulse width constraints (dotted red lines).

#### 2.5. Hierarchical design style

On the other end of design styles is the hierarchical design style which is much more flexible in terms of the circuit structure. Standard cells are put together in a hierarchical manner to create meaningful circuits that match a given specification. Silistix UK Ltd. is a startup which provides solutions for self-timed on-chip interconnect. They use a standard cell library with some added special cells such as Celements and mutual exclusion elements necessary in asynchronous design [2]. They design delay insensitive circuits which are premised on the fact that they will function correctly regardless of the delays on the gates and the wires. An example circuit is the well-known sequencer also known as the Q-element [11] that implements enclosed handshaking on channel B and is shown in Figure 2-1.

Figure 2-6: S-element with (a) RT constraints and (b) timing diagram

The S-element has two internal timing constraints (highlighted in red and green) and one external timing constraint (blue).

- Internal constraint 1 (red): This constraint forks from input Areq of the S-element. Input i0 of the AND gate should fall before input i1 of the AND gate rises. If this constraint is not satisfied, the AND gate can turn on creating a false request on channel B.

- Internal constraint 2 (green): This constraint forks from input Back of the Selement. Input i0 of the NOR gate should rise before input i1 of the NOR gate falls. If this constraint is not satisfied, the NOR gate can evaluate to a logic '1' acknowledging falsely the completion of the handshake on channel B.

- External constraint (blue): This constraint forks from input Back of the S-element. Input u0 of the asymmetric C-element should fall before input i0 of the C-element rises in order to return the S-element back to its reset state. If this constraint is not satisfied, then a new request on channel A can be lost. The dashed arrow indicates that the constraint traverses paths in the environment of the S-element.

# Chapter 3

# 3. Library Characterization for SSTFB

The industry standard format for representing delay and power information of a library is the Liberty format. It supports several delay models of which we chose the non-linear delay as it provides a reasonable tradeoff between accuracy and complexity. This delay model uses lookup tables indexed by input slew and/or load capacitance. There are four main steps involved in delay and power characterization. The first is defining timing arcs for the cell being characterized. The second is creating a suitable simulation environment for spice measurements. The third step is measuring power consumption and the last step is measuring pin capacitances. In addition, we would like to automate this flow as much as possible. Unlike synchronous standard cells, for which commercial library characterization tools are available, the effort has to be implemented from scratch and semi-automated. The following three subsections address these challenges and how they were solved in more detail. In addition, it is necessary to measure the correct supply currents to accurately characterize internal power.

## 3.1. Defining Timing Arcs

A set of timing arcs need to be identified that capture the behavior of SSTFB. The causality between the timing arcs is formalized in a marked graph. As an example, Figure 3-1 illustrates the marked graph model of a buffer cell surrounded by a bit generator and bucket in which the specific data rails have been abstracted. Our future plans include constraining the short circuit between senders and receivers. This requires detailed knowledge of when the driver circuits are active and motivated us to explicitly model the internal signals S and A as extra bi-directional pins. Notice that the dashed edges represent the behavior of the environment whereas the solid edges refer to the behavior of the cell. The '+' symbol is used to indicate a rising transition and data going valid, '-' for a falling transition and data going neutral, '0Z' for a low to tri-state transition and '1Z' for a high to tri-state transition.

Figure 3-1: Abstract marked graph of a SSTFB buffer surrounded by a bit generator and generator

## **3.2.** Creating a Simulation Environment

#### **3.2.1. Input waveforms**

Traditionally, the input driver uses a ramped linear waveform which is not desirable as it can by itself contribute to 5-10% delay error. Commercial library

characterization tools use one of two approaches to generate real-world input waveforms: the pre-driver method or a pre-driver generated 'real' non-linear waveform. A buffer is often recommended for use as the pre-driver cell as shown in Figure 3-2(a). For asynchronous circuits, special cells are needed generate and consume input and output tokens to/from the circuit under test (CUT). Commonly, these cells which form the environment around the CUT are called bitgen and bucket respectively, shown in Figure 3-2(b). The bitgen implicitly takes care of the input waveform generation. The input slew is controlled by an adjustable capacitor  $C_S$  and the output load is controlled by the capacitor  $C_L$ .

(b) test environment for SSTFB

# Figure 3-2: Test setup for (a) synchronous circuits (b) asynchronous circuits 3.2.2. Input Slew and Load Capacitances

The selection of input slew and load capacitance indices along with creating real-world input waveforms directly impacts the accuracy of the characterization. Delay behaves non-linearly and non-monotonically with input slew. The design usage space should be bounded by carefully selecting the minimum and maximum input slew and load capacitance values to minimize delay calculation error due to interpolation and extrapolation. The output load model can be simplified by assuming a lumped capacitance. The output load index must be based on the cell drive strength. The tables should have enough points for both input slew and output load index selections so as to cover non-linear or non-monotonic regions.

In the proposed flow, the minimum load capacitance was zero and the maximum was calculated such that the cell operated within pre-determined voltage swing levels. The input slew values were computed for each cell in the library based on the selected load capacitance values. The load capacitance on internal pins is fixed. Consequently timing arcs from input pins to the S and A pins need only be modeled as a 1D table (1x6) based on the input slew. However, arcs from the state pins S to the output pins R are modeled as a 2D table (6x6) based on both slew on S and output load.

#### **3.3. Measuring power**

The main challenges for power characterization are partitioning the currents drawn through the supply amongst timing arcs for the dynamic component, modeling short circuit current and the effects of crosstalk. The Liberty format measures internal energy per timing arc which includes short-circuit power. Power analysis tools convert this internal energy to internal power by dividing by the system cycle time. They also add short-circuit energy and switching energy, the latter calculated as the energy required for switching the total net capacitance on the nets. The dynamic internal energy component of energy for an arc can be calculated using the following equation:

$$E_{arc} = \frac{\left(\left(I_{vdd/gnd} - I_{leakge}\right) * Vdd\right) * T}{N}$$

(1)

where,  $I_{vdd/gnd}$  is the average current measured through specific voltage sources associated with the timing arc,  $I_{leakage}$  is the current measured when the circuit is idle, Vdd is the supply voltage, T is total simulation trace time and N is the number of tokens processed in time T. We added 0V voltage sources to Vdd segments of the extracted placed-and-routed netlist to measure the currents responsible for charging internal cell nodes. We added 0V voltage sources to segments of Gnd to measure the short-circuit current associated with charging output nodes (e.g., the R0/R1 nets). As an example, consider the SCD in a buffer. To measure the internal energy associated with the timing arc S0<sup>-</sup>  $\rightarrow$  A<sup>+</sup>, we insert a 0V source as shown in Figure 3-3.

Figure 3-3: Addition of a 0V source to measure the internal energy associated with the timing arc S0<sup>-</sup>  $\rightarrow$  A<sup>+</sup>

In general, the measured currents associated with each token value can be partitioned among the associated timing arcs that must occur for each such token processed. For cells with a single-input channel, however, we partitioned currents into one power arc for each output accessed by an arbitrarily-chosen single related pin. For cells with multiple input channels in which multiple power arcs existed for a given output, we accounted for the power of all arcs in each arc. In this case, the power analysis tool chooses one such power arc depending on the timing of the related pins. This leads to a small amount of error because we are essentially assuming the slew on all input channels is identical.

# 3.4. Measuring Pin Capacitances

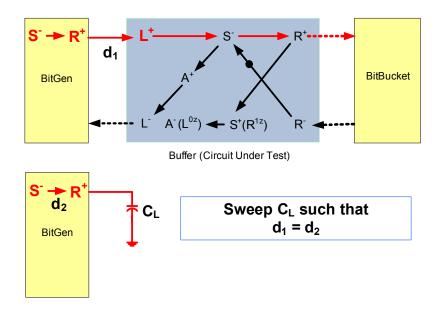

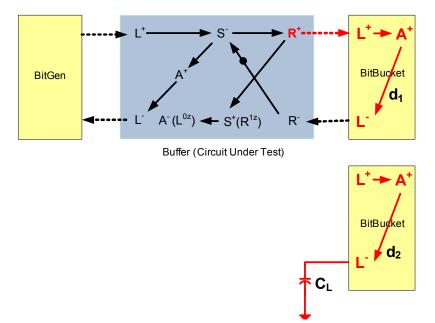

The liberty format requires pin capacitances for all input/output pins. A standard delay matching technique was used to measure the pin capacitances as shown in

Figure 3-4 and Figure 3-5. To measure the pin capacitance of pin A0 of the buffer, the delay  $d_1$  from S0<sup>-</sup> of the bitgen to A0<sup>+</sup> of the buffer was measured. The buffer was then replaced by a variable capacitor and its value swept until delay  $d_2$  from S0<sup>-</sup> of bitgen to R0<sup>+</sup> of bitgen matched delay  $d_1$ . The capacitance at which the delays match gives the capacitance of pin A0.

Figure 3-4: Measuring pin capacitance of pin A0 of a buffer

Figure 3-5: Measuring pin capacitance of pin R0 of a buffer

To measure the pin capacitance of pin R0 of the buffer, the delay  $d_1$  from  $A^+$  of the bucket to  $R0^-$  of the buffer was measured. The buffer was then replaced by a variable capacitor and its value swept until delay  $d_2$  from  $A^+$  of the bucket to  $A0^-$  of

the bucket matched delay  $d_1$ . The capacitance at which the delays match gives the capacitance of pin R0. For proof of concept, the delays were matched only at 50% of supply voltage but ideally the delay should be matched at several points for a more accurate capacitance value.

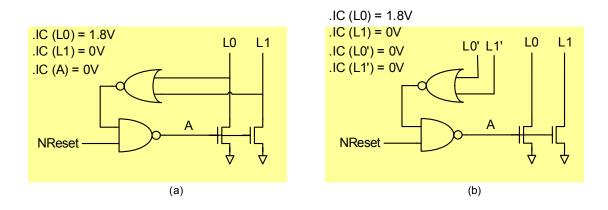

There are some subtleties related to HSpice that should be taken care of while measuring the pin capacitances on channel R. In the second set-up where a load capacitor  $C_L$  is attached to the left channel of the bit bucket, one of the rails of the left channel should be initialized to the logic value '1' using the .IC card in HSpice. Also, the internal pin A should be initialized to the logic value '0'. At time 0, the NOR gate shown in Figure 3-6 (a) evaluates to a '0' causing the NANd gate to evaluate to a '1'. This causes a fight on the internal pin A creating a fake rising slew on it. Also, the state of NReset does not impact the value of pin A. If fake input channel rails L0' and L1' are created and tied low as in Figure 3-6 (b), the output of the NOR gate doesn't control the NAND gate anymore. Initially, NReset is held high so as to prevent the bucket from consuming the token on the false rail L0 as A is 0. Once NReset is pulled low, the NAND gate turns on causing A to rise and pull the false rail L0 low. Pin A now has a real rising slew on it.

Figure 3-6: SSTFB BitBucket schematic (a) incorrect HSpice set-up (b) correct HSpice set-up

## 3.5. Library Generation

Using the above concepts, the flow illustrated in Figure 3-7 is used for complete timing and power characterization. Spice netlists of the cells were fed to Hspice along with perl-generated stimulus files. These stimulus files contain measure statements for delay, slew, and energy. Data is extracted from the output of Hspice which is in the .mt# file format and automatically converted to the liberty format. For ease of characterization, we sometimes assumed symmetry to estimate delays and slews of one data rail using measured data from the other rail, introducing a small amount of error due to small differences in the layout between rails.

**Figure 3-7: Characterization flow**

#### **3.6. Validation Results**

To validate the quality of our characterization, we used several representative unbalanced non-linear pipelines commonly seen in asynchronous design (Figure 3-8). The validation flow is shown in Figure 3-9. Cadence's SoC Encounter is used to perform delay calculation for each timing arc instance in the routed netlist using the liberty description, recording the resulting arc delays in a standard delay format (.sdf) file. The .sdf file along with the Verilog netlist is simulated in Cadence's NC-Verilog simulator. This generates a timing-accurate value change dump (.vcd) file that records the signal activity. The .vcd file is then fed back into SoC Encounter to compute simulation-based power analysis. The results of the simulation-based timing and power analysis are compared to golden Hspice simulations.

Figure 3-8: Unbalanced non-linear pipelines used for validating the characterization flow.

Figure 3-9: Validation flow

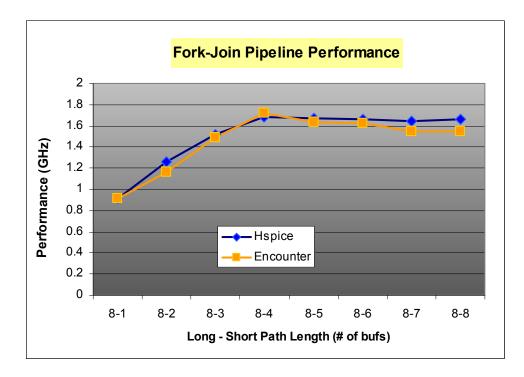

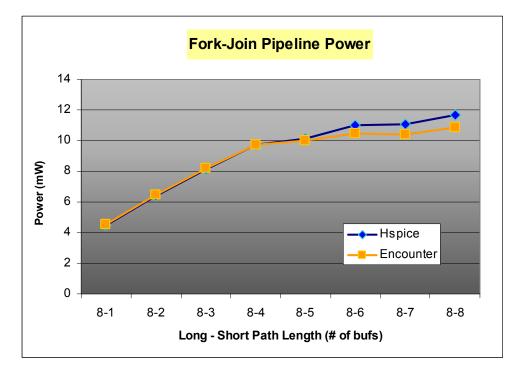

Figure 3-10 and Figure 3-11 show the performance and power dissipation as measured by Hspice and the Encounter-based flow using our prototype SSTFB library. The performance plot shows an interesting counter-intuitive result that maximum throughput is achieved when the short and long paths of the fork-join structure are somewhat unbalanced, i.e., the short path has 4 buffers while the long path has 8 buffers. This fact can be attributed to the "free-slack" associated with the buffers that are faster than the FORK and JOIN cells. More balanced fork-join pipelines are slightly slower due to increased wire delay and consume more energy.

The experimental results show a maximum error between the encounter estimated and Hspice golden numbers of 7.1%. We believe much of this error can be attributed to the limited slew propagation during SDF generation due to the loops and bi-directional pins in the SSTFB .lib model.

Figure 3-10: Fork-join pipeline experiment – performance

Figure 3-11: Fork-join pipeline experiment - power

# Chapter 4

# 4. Static Timing Analysis for Asynchronous Circuits

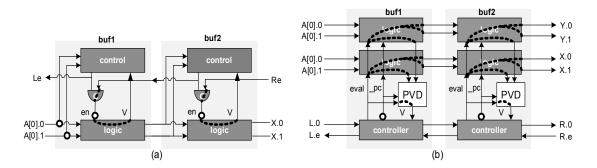

PCHB and MLD templates are representative asynchronous circuit templates with timing loops and relative timing constraints but without the more complex features like bi-directional pins present in SSTFB. Due to this reason we chose to demonstrate the STA flow on PCHB and MLD templates and leave the extension to SSTFB as future work. Three steps constitute the static timing analysis flow for any template based design. The first step is to capture the timing constraints (relative and minimum pulse width) within PrimeTime. The second step is to break combinational loops which should be done in a manner that doesn't break paths of interest. The last step is to do performance verification. All these steps are described in detail in the following sections. For simplification, the various steps of the flow are explained using three-stage PCHB and MLD linear pipelines. For the DI circuits at Silistix, only constraint verification was carried out.

#### **4.1. Modeling relative timing constraints**

#### 4.1.1. Non-sequential data checks

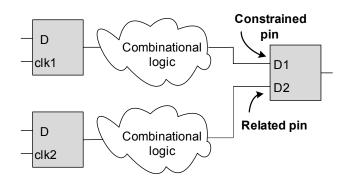

A hold or a setup check between two data signals is called a non-sequential constraint [14]. Synopsys PrimeTime allows the designer to check such a constraint using a command called *set data check*. In the synchronous world, one of these data

signals D1 might be used to capture data on the other data signal D2 as shown in Figure 4-1. The command shown will check if the rising transition on D1 occurs a setup time 1.5ns before the rising edge on D2. The command constrains pin D1 relative to pin D2 and thus the names constrained pin and related pin. This command compares the slowest path to the constrained pin to the fastest path to the related pin to verify that the specified setup time was met. This is synonymous to checking if the latest arriving data signal sets up a setup time before the earliest edge of the clock. For a more accurate post-layout analysis, PrimeTime's on-chip variation (OCV) mode can be used to account for PVT variations between the two paths of interest.

set\_data\_check -rise\_to D2 -rise\_from D1 -setup 1.5

## Figure 4-1: Non-sequential data to data check

The relative timing constraints stemming from a fork can be easily modeled using the set\_data\_check command and modeling the ends of the fork as constrained and related pins. The start of the fork is commonly referred to as the point of divergence (POD). In the case of PCHB and MLD, the data rails are the constrained pins and the enable pins 'en' are the related pins. The path from the POD to the constrained pin is referred to as the short path and the path from the POD to the related pin is referred to as the long path. The commands for a three stage PCHB pipeline, a three stage MLD pipeline and the S-element are listed in Figure 4-2. There are six RT constraints for the three-stage PCHB pipeline and four RT constraints for the threestage MLD pipeline. For the purpose of illustration, an arbitrary setup margin of 0.5ns was chosen for the data checks.

> set\_data\_check -rise\_from buf1/en -fall\_to buf1/A[0].0 -setup 0.5 set\_data\_check -rise\_from buf1/en -fall\_to buf1/A[0].1 -setup 0.5 set\_data\_check -rise\_from buf2/en -fall\_to buf2/A[0].0 -setup 0.5 set\_data\_check -rise\_from buf3/en -fall\_to buf3/A[0].0 -setup 0.5 set\_data\_check -rise\_from buf3/en -fall\_to buf3/A[0].0 -setup 0.5 set\_data\_check -rise\_from buf3/en -fall\_to buf3/A[0].1 -setup 0.5 (a) set\_data\_check -rise\_from buf2/eval -fall\_to buf2/A[0].0 -setup 0.5 set\_data\_check -rise\_from buf2/eval -fall\_to buf2/A[0].1 -setup 0.5 (b) set\_data\_check -rise\_from i3/i1 -fall\_to i3/i0 -setup 0.5 set\_data\_check -rise\_from i3/i1 -fall\_to i3/i0 -setup 0.5 (c)

# Figure 4-2: Modeling the relative timing constraints using set\_data\_check for (a) PCHB template (b) MLD template (c) S-element

### 4.1.2. Associated challenges

There are several challenges involved in modeling RT constraints in PrimeTime. Typical STA tools that are built with synchronous circuits in mind expect flip flops enabled by a global clock signal at the launch and capture points of data. The timing constraint is that the data reaches its capture point from its launch point in less than a clock cycle. Without a global clock signal and flip flops to create data launch and capture points, it is impossible to model the constraints described in Chapter 2 in PrimeTime.

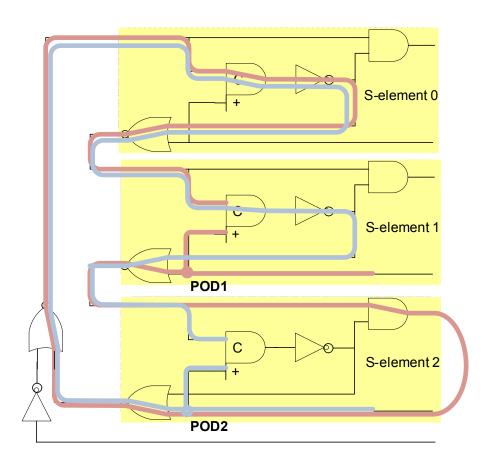

One approach to this is to model the POD and the POC as the launch and capture points respectively by creating virtual clocks on the PODs. Creating multiple clocks in the design poses other challenges. First, the related or the constrained pins can now originate from different clock domains in which case PrimeTime will check the paths separately and report all the combinations. In the case of the forks, both the short and the long paths start at the same point: the POD. Second, creating virtual clocks on pins in the design creates cut points in the corresponding timing graph. Thus any virtual clock that intersects a constraint causes a timing path in that constraint to be broken making it impossible to verify the two constraints in the same PrimeTime run. This problem is illustrated in Figure 4-3 where the two forks yield overlapping constraints. Specifically, the POD of the blue constraint associated with the fork in S-element 2 (POD2) intersects the long path of the red constraint associated with the fork in S-element 1. This problem is revisited in Section 4.3.

The solution to the first challenge is to specify the launching clock explicitly using the –clock option in the data check command. This has the added benefit of reducing the number of paths PrimeTime needs to analyze potentially reducing the run time. The downside is that the slew information on the POD is lost as the tool creates an ideal clock which can lead to over optimistic results. This effect can be mitigated by moving the POD back one level for every stage except the first. Figure 4-4 shows the modified commands that specify the clock domains and reflect the new PODs in the case of PCHB. An important thing to note here is that now there are two paths to the related pin: one through the true rail and one through the false rail. While checking for the constraint on the false rail, the path from the POD through the true rail should be disabled and vice versa to generate the correct timing reports.

set\_data\_check -clock buf1/A[0].0 -rise\_from buf1/en -fall\_to buf1/A[0].0 -setup 0.5 set\_data\_check -clock buf1/en -rise\_from buf2/en -fall\_to buf2/A[0].0 -setup 0.5 set\_data\_check -clock buf2/en -rise\_from buf3/en -fall\_to buf3/A[0].1 -setup 0.5 (a)

set\_data\_check -clock buf1/pc -rise\_from buf2/eval -fall\_to buf2/A[0].0 -setup 0.5 (b)

# Figure 4-4: Modified set\_data\_check commands for (a) PCHB template (b) MLD template and (c) S-element

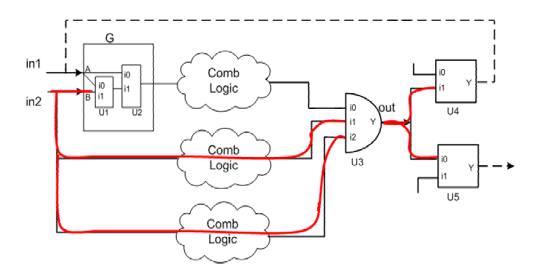

The external constraint on the S-element described earlier in Section 2.5. requires special handling as the long path can traverse many gates through many levels of hierarchy before converging at the POC. The long path may also branch off several times causing PrimeTime to analyze all the possible paths between the POD and the POC in order to find the fastest slow path. This can result in an exponential increase in run time and render the approach useless. In most cases with careful placement and routing, a few gate delays on the slow path provide enough setup margins. Thus the related pin can be moved closer to the POD reducing the number of paths that need to be inspected. This new related pin will be referred to as the fake related pin throughout the rest of the document. Starting close to the POD and moving away from it, multiple fake related pins can be selected and set\_data\_checks issued for each so that a good range of gate delays is included to make sure that the constraint passes verification in a

single run and false negatives avoided. If a fork is encountered, paths on all branches should be traversed. In the example shown in Figure 4-5, where the POD is pin in2 and the POC is gate G, some of the possible fake related pins are U3/i1, U3/i1, U4/i1 and U5/i0.

Figure 4-5: Multiple fake related pins per constraint

It is also important to note here that the –clock option does not allow us to specify the direction of the clock transition we are interested in. Thus it may find that the fastest slow path is from a falling edge of the clock when we are interested in the rising edge of the clock. This can easily be taken care of by disabling all the paths from the falling edge of the clock within PrimeTime.

# 4.2. Modeling the minimum pulse width constraints

The minimum pulse width constraint in MLD spans a timing loop as shown in Figure 2-5. This means that the constraint needs to be decomposed into at least two

segments depending on how the loop is broken. The natural approach to modeling this in PrimeTime is by constraining it as a minimum delay constraint using the command set\_min\_delay. An example command set is shown in Figure 4-6 where the loop is broken at the boundaries of the control block yielding two minimum delay constraints.

set\_min\_delay1 -fall\_from buf1/buf\_v\_logid\_pc -fall\_to buf1/buf\_v\_logid/V

set\_min\_delay1 -fall\_from buf1/buf\_v\_logid/V -rise\_to buf1/buf\_v\_logic/\_pc

## Figure 4-6: Modeling minimum pulse width constraint

# 4.3. Breaking timing loops

PrimeTime has two loop breaking techniques: static loop breaking and dynamic loop breaking. With static loop breaking, the tool automatically breaks loops by disabling timing arcs during the initial timing analysis. These loop breaks persist throughout the primetime run until another run is initiated. Dynamic loop breaking on the other hand does not permanently disable any timing arcs and guarantees that all paths will be reported. Both these techniques don't work for asynchronous circuits due to several reasons.

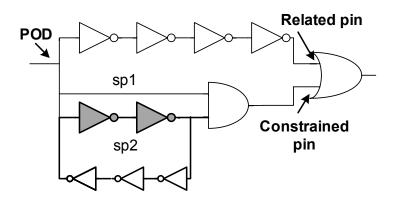

Static loop breaking has the potential for disabling paths of interest resulting in incorrect timing reports. Consider the example in Figure 4-7 where there are two paths to the constrained pin, labeled sp1 and sp2. There is also a combinational loop that includes path sp2 which is the slowest short path. If PrimeTime disables a timing path through any of the inverters in path sp2, then path sp1 will become the new slowest short path resulting in an incorrect data check report. If there was only one short path sp2, then PrimeTime Would not find any paths for the data check report.

**Figure 4-7: Static loop breaking**

The problem with dynamic loop breaking is that the loop breaking flexibility is accompanied by heavy memory usage and large run-time making it impractical for even a medium sized design. Due to these reasons, we are forced to break loops explicitly by disabling timing paths carefully so as not to break any paths of interest. This is done with the command *set disable timing*.

### **4.3.1.** Loop breaks for template-based designs

The regular structure of the circuits built using PCHB and MLD templates proves to be advantageous while breaking timing loops. By disabling certain timing arcs for some of the library cells, all timing loops can be broken without breaking any paths of interest. Figure 4-8 shows the loop breaks (dotted lines) for PCHB and MLD. The dots indicate the location of the clocks.

Figure 4-8: Clocks and loop breaks for (a) PCHB and (b) MLD templates

### 4.3.2. Loop breaks for hierarchical design style based circuits

The lack of any regular structure poses a bigger challenge in loop breaking. In a medium sized circuit, tens of thousands of feedback loops exist [9] making it very likely that there will be overlaps between loop breaks and timing constraints that need to be verified. These overlaps are in addition to the overlaps caused due to intersecting constraints discussed in section 4.1.2. A naïve solution to the overlapping constraint problem is to create and remove virtual clocks on the fly during a PrimeTime run. But this can be very costly in terms of run-time as every time a clock is created or removed, the timing graph internal to the tool changes evoking time consuming timing updates. Instead, a methodology is required which identifies a set of loop breaks such that a minimum number of constraints are disturbed and partitions the constraints into an optimal number of non-overlapping sets based on the loop breaks. A prototype flow was developed as part of the internship to demonstrate the feasibility of the proposed methodology.

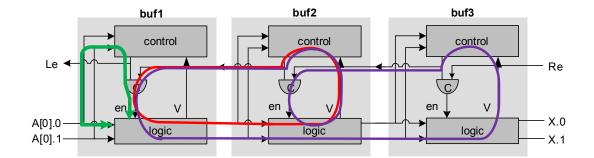

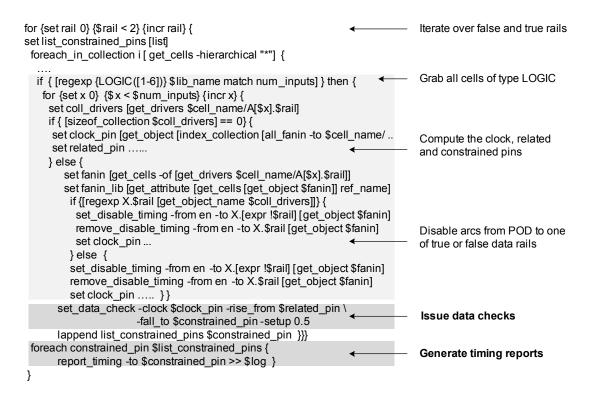

#### **4.3.3.** Fully automated scripts

PrimeTime supports Tcl and many useful internal commands which can be used to gain information about the design being verified. Portions of the fully automated RT constraints verification scripts for PCHB is shown in Figure 4-9. Internal PrimeTime commands are used to get all cells of type LOGIC, get connectivity information to determine the POD, the related and the constrained pins to create the constraints and apply them automatically. Some cells such as token buffers need special handling and are not shown in the figure for simplicity. Note the first for loop that divides the verification of the constraints into two sets. One set for the false rails and the other for the true rails. This is because the long path traverses the data rails and the timing arcs from the POD to one of the rails is disabled However, in the case of MLD all the constraints can be verified in a single set as the long path does not go through the data rails. This also enables us to generate the timing reports associated with both the rails at once at the end of the script. RT verification and performance verification scripts for PCHB and MLD are written in a similar manner. In the case of Silistix' circuits, a script that verified the relative timing constraints associated with all

the S-elements in the design was developed. The script partitions the constraints into non-overlapping sets by comparing the POD of a constraint to all the related pins associated with all the other constraints. A match means that the two constraints should be put in different sets. With this approach, a timing update per set of constraints is required compared to a timing update per constraint which leads to large run times. Please refer to Appendix A for all the scripts.

Figure 4-9: Relative timing constraints verification script for PCHB

# 4.4. Modeling performance

As mentioned earlier, the cycle time of these pipelines is reduced to verifying the timing of the loops. Because of the limitations of STA tools, these timing loops need to be decomposed into two or more segments by creating cut points. The delay of these segments should then be verified using maximum delay constraints with the command set\_max\_delay. The approach then is as follows:

- Identify a minimal set of cut-points that break all timing loops.

- Constrain all segments with a maximum delay constraint where the maximum delay value is the sum of the specified delays of all timing arcs in the segment

- If all segments meet timing, then all cycle time constraints are met.

Notice that the latency of a design is simultaneously verified as long as segments that begin at primary inputs and/or end at primary outputs are identified, constrained, and verified. We note that this decomposition does force some conservativeness as time borrowing across segments is disallowed. In the case of the PCHB pipeline, creating cut-points at all the enable pins of the logic blocks cuts all the timing loops.

# 4.5. Results

The proposed flow was fully automated using tcl and run on several ISCAS benchmarks that were synthesized to a synchronous image netlist and then automatically translated to PCHB and MLD pipelines. The run times for constraint verification and performance verification on a Sun Blade 1000 machine with 2GB RAM are shown in Table 1 and Table 2. Sample timing reports for relative timing constraints and performance verification for the simple linear pipeline test cases are shown in Figure 4-10 and Figure 4-11. For the purpose of illustration, an arbitrary setup margin of 0.5ns was used for constraint verification and an arbitrary maximum delay value of 2ns was used to constrain the segments for performance verification. In this example, the RT constrain is satisfied with a left-over margin of 0.2ns for PCHB and 0.42ns for MLD. The first half of the constraint verification report shows the short path and the second half of the report shows the long path for the data check. In the case of performance verification, the segment shown satisfies the maximum delay constraint with a left-over margin of 0.39ns for PCHB and 1.93ns for MLD.

Table 1: Run times for RT constraints verification

|           | PCH         | B        | MLD         |          |  |

|-----------|-------------|----------|-------------|----------|--|

| ISCAS     | No. of      | Run Time | No. of      | Run Time |  |

| benchmark | Constraints | (sec)    | Constraints | (sec)    |  |

| s298      | 230         | 8        | 212         | 5        |  |

| s400      | 374         | 14       | 296         | 8        |  |

| s1423     | 1616        | 115      | 1456        | 63       |  |

| c3540     | 6870        | 17 min   | 7560        | 11 min   |  |

Table 2: Run times for performance verification

|           | РСН         | B        | MLD         |             |  |

|-----------|-------------|----------|-------------|-------------|--|

| ISCAS     | No. of      | Run Time | No. of      | Run Time    |  |

| benchmark | Constraints | (sec)    | Constraints | (sec)       |  |

| s298      | 963         | 6        | 4613        | 18          |  |

| s400      | 1447        | 12       | 6268        | 18          |  |

| s1423     | 4574        | 41       | 112727      | 5 min       |  |

| c3540     | 23414       | 210      | 747426      | 1 hr 19 min |  |

| Startpoint: buf1/buf_logic/en<br>(clock source 'buf1/buf_logic/en')<br>Endpoint: buf2/buf_logic<br>(rising edge-triggered data to data<br>buf1/buf_logic/en)<br>Path Group: buf1/buf_logic/en<br>Path Type: max | a check                 | clocked by                 | Startpoint: buf1/controller/_pc<br>(clock source 'buf1/controller/_pc')<br>Endpoint: buf2/buf_v_logic<br>(rising edge-triggered data to data<br>buf1/controller/_pc)<br>Path Group: buf1/controller/_pc<br>Path Type: max |                       | clocked b                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------|

| Point                                                                                                                                                                                                           | Incr                    | Path                       | Point                                                                                                                                                                                                                     | Incr                  | Path                       |

| clock buf1/buf_logic/en (fall edge)<br>clock source latency<br>buf1/buf_logic/en (synthesis.qdi.logic1.LOGIC                                                                                                    | 0.00<br>0.00<br>(1_1.1) | 0.00<br>0.00               |                                                                                                                                                                                                                           | 0.00<br>0.00<br>RL.1) | 0.00<br>0.00               |

| buf1/buf_logic/X.0 (synthesis.qdi.logic1.LOGI                                                                                                                                                                   |                         | 0.00 f                     | buf1/buf_v_logic/X.0 (synthesis.mld.logic1.V_L                                                                                                                                                                            |                       |                            |

| buf1/X.0 (buf)<br>buf2/A[0].0 (buf)                                                                                                                                                                             | 0.37<br>0.00<br>0.00    | 0.37 f<br>0.37 f<br>0.37 f | buf1/R[0] (mld_buf_l1)                                                                                                                                                                                                    | 0.26<br>0.00<br>0.00  | 0.26 f<br>0.26 f<br>0.26 f |

| buf2/buf_logic/Á[0].0 (synthesis.qdi.logic1.LO                                                                                                                                                                  | GIC1_1.<br>0.00         | 0.37 f                     |                                                                                                                                                                                                                           | /_LOGI0<br>0.00       | 0.26 f                     |

| data arrival time                                                                                                                                                                                               |                         | 0.37                       | data arrival time                                                                                                                                                                                                         |                       | 0.26                       |

| clock buf1/buf_logic/en (fall edge)<br>clock source latency<br>buf1/buf_logic/en (synthesis.gdi.logic1.LOGIC                                                                                                    | 0.00<br>0.00            | 0.00<br>0.00               |                                                                                                                                                                                                                           | 0.00<br>0.00          | 0.00<br>0.00               |

| buf1/buf_logic/X.0 (synthesis.qdi.logic1.LOGI                                                                                                                                                                   | 0.00<br>C1_1.1)         | 0.00 f                     | buf1/buf_v_logic/V (synthesis.mld.logic1.V_LC                                                                                                                                                                             | 0.00<br>0GIC1_1       |                            |

| buf2/buf_ctrl/en (synthesis.qdi.special.CTRL1                                                                                                                                                                   | 0.37<br>1.1)<br>0.56    | 0.37 f<br>0.93 r           | buf2/controller/L.e (synthesis.mld.special.CTR                                                                                                                                                                            | 0.40<br>L.1)<br>0.27  | 0.40 f<br>0.68 r           |

| buf2/buf_ctree/x (synthesis.qdi.special.CTRE                                                                                                                                                                    | 0.14                    | 1.07 r                     |                                                                                                                                                                                                                           | 0.23                  | 0.90 r                     |

| buf2/buf_logic/en (synthesis.qdi.logic1.LOGIC                                                                                                                                                                   | 1_1.1)<br>0.00          | 1.07 r                     | buf2/controller/eval (synthesis.mld.special.CTF                                                                                                                                                                           | RL.1)<br>0.27         | 1.17 r                     |

| data check setup time<br>data required time                                                                                                                                                                     | -0.50                   | 0.57<br>0.57               |                                                                                                                                                                                                                           | 0.00                  | 1.17 r                     |

| data required time<br>data arrival time                                                                                                                                                                         |                         | 0.57<br>-0.37              | data check setup time<br>data required time                                                                                                                                                                               | -0.50                 | 0.67<br>0.67               |

| slack (MET)                                                                                                                                                                                                     |                         | 0.20                       | data required time<br>data arrival time                                                                                                                                                                                   |                       | 0.67<br>-0.26              |

|                                                                                                                                                                                                                 |                         |                            | slack (MET)                                                                                                                                                                                                               |                       | 0.42                       |

| (a)                                                                                                                                                                                                             |                         | (b)                        |                                                                                                                                                                                                                           |                       |                            |

Figure 4-10: Relative timing constraints verification report for (a) PCHB and (b) MLD templates

Startpoint: buf1/buf1\_logic/en (internal path startpoint) Endpoint buf3/buf1\_logic/en (internal path endpoint) Path Group: \*\*default\*\* Path Type: max

| Point                                        | Incr    | Path    |

|----------------------------------------------|---------|---------|

| input external delay                         | 0.00    | 0.00 r  |

| buf1/buf1_logic/en (synthesis.qdi.logic1.LOG | IC1_1.1 | )       |

|                                              | 0.00    | 0.00 r  |

| buf1/buf1_logic/X.0 (synthesis.qdi.logic1.LO | GIC1_1. | 1)      |

|                                              | 0.39    | 0.39 r  |

| buf1/X.0 (buf)                               | 0.00    | 0.39 r  |

| buf2/A[0].0 (buf)                            | 0.00    | 0.39 r  |

| buf2/buf1_logic/X.1 (synthesis.qdi.logic1.LO | GIC1_1. | 1)      |

|                                              | 0.37    | 0.76 r  |

| buf2/X.1 (buf)                               | 0.00    | 0.76 r  |

| buf3/A[0].1 (buf)                            | 0.00    | 0.76 r  |

| buf3/buf1_logic/V (synthesis.qdi.logic1.LOGI | C1_1.1) |         |

|                                              | 0.32    | 1 .09 r |

| buf3/buf1_ctrl/en (synthesis.qdi.special.CTR | L11.1)  |         |

|                                              | 0.31    | 1 .40 f |

| buf3/buf1_ctree/x (synthesis.qdi.special.CTF | REE2.1) |         |

|                                              | 0.22    | 1 .61 f |

| buf3/buf1_logic/en (synthesis.qdi.logic1.LOG | IC1_1.1 | )       |

|                                              | 0.00    | 1.61 f  |

| data arrival time                            |         | 1.61    |

|                                              |         |         |

| max_delay                                    | 2.00    | 2 .00   |

| output external delay                        | 0.00    | 2.00    |

| data required time                           |         | 2.00    |

|                                              |         |         |

| data required time                           |         | 2.00    |

| data arrival time                            |         | -1.61   |

|                                              |         |         |

| slack (MET)                                  |         | 0.39    |

| (a)                                          |         |         |

| Point                                         | Incr  | Path    |

|-----------------------------------------------|-------|---------|

| input external delay                          | 0.00  | 0.00 r  |

| buf2/buf_v_logic/X.0 (synthesis.mld.logic1.V_ | LOGIC | 1_1.1)  |

|                                               | 0.00  | 0 .00 r |

| buf2/R[0] (mld_buf_l1)                        | 0.00  | 0 .00 r |

| buf3/L[0] (mld_buf_l1)                        | 0.00  | 0 .00 r |

| buf3/buf_v_logic/X.1 (synthesis.mld.logic1.V_ | LOGIC | 1_1.1)  |

|                                               | 0.07  | 0.07 r  |

| data arrival time                             |       | 0.07    |

| max_delay                                     | 2.00  | 2.00    |

| output external delay                         | 0.00  | 2.00    |

| data required time                            |       | 2.00    |

| data required time                            |       | 2.00    |

| data arrival time                             |       | -0.07   |

| slack (MET)                                   |       | 1.93    |

(b)

# Figure 4-11: Performance verification report for (a) PCHB and (b) MLD templates

# Chapter 5

# **5.** Conclusions and Future Work

A fully characterized asynchronous library not only supports back-annotated simulation-based power and timing analysis. It also enables timing driven place and route, performance and power driven synthesis and ECO flows. Moreover, characterized asynchronous libraries are a necessary pre-cursor to extending STA-based timing sign-off to these designs. The work presented in this thesis demonstrates the issues, feasibility, and potential accuracy associated with characterizing static STFB circuits. This is quite promising because the SSTFB circuits have among the most complex timing relationships of the many different proposed asynchronous design styles and have promising characteristics for application in low-power high-performance SoC interconnects.

This thesis also presents a fully-automated flow for pre and post layout static timing analysis for two template-based asynchronous circuits using a commercial STA tool. The proposed flow is not specific to a design and can be used to verify the timing of any design built using PCHB or MLD templates. A prototype constraint verification flow for hierarchical design style based asynchronous circuits is also presented. The performance verification flow verifies a fixed delay model that allows time borrowing across gates in a segment but not across segments. Potential extensions to this work include the application of the timing constraints to performance-driven place-and-route as well as the application of both the characterization and the static timing analysis methodologies to other non-standard circuits. This includes extending our STA flow to single-track templates with bi-directional pins, such as SSTFB, and bundled-data designs, as well as synchronizers typically found in SoC systems. In addition, a tighter connection between the STA flow and automatic generation of relative-timing constraints to verify the completeness of the constraints tested, actively manage the run-times of the STA tool, and reduce the conservativeness of the constraints would also be valuable.

# Bibliography

- N. Andrikos, L. Lavagno, D. Pandini, C. P. Sotiriou, "A Fully-Automated Desynchronization Flow for Synchronous Circuits", *Design Automation Conference*, pp. 982-985, June 2007

- [2] W.J.Bainbridge, A.Bardsley, R.W.McGuffin, "System-on-Chip Design using Self-timed Networks-on-Chip", Whitepaper, www.silistix.com.