## TEMPLATE BASED ASYNCHRONOUS DESIGN

By

Recep Ozgur Ozdag

A Dissertation Presented to the FACULTY OF THE GRADUATE SCHOOL UNIVERSITY OF SOUTHERN CALIFORNIA In Partial Fulfillment of the Requirements for the Degree DOCTOR OF PHILOSOPHY (ELECTRICAL ENGINEERING)

November 2003

Copyright 2003 Recep Ozgur Ozdag

# Contents

| List o | f Tables                                                      | V        |

|--------|---------------------------------------------------------------|----------|

| List o | f Figures                                                     | V        |

| Abstr  | act                                                           | 1X       |

| 1. I   | ntroduction                                                   | 1        |

| 1.1    | Asynchronous Circuit Design Flow                              | <i>6</i> |

| 1.2    | Expected Contributions of the Thesis                          |          |

| 1.3    | Thesis Organization                                           |          |

| 2. B   | ackground                                                     | 11       |

| 2.1    | Data Encoding Styles                                          |          |

| 2.2    | Handshaking Styles                                            |          |

| 2.3    | Delay Models                                                  |          |

| 2.4    | Synthesis Based Design                                        |          |

| 2.4.1  | •                                                             |          |

| 2.4.2  |                                                               |          |

| 2.4.3  | 8                                                             |          |

| 2.5    | Template-Based Design                                         |          |

| 2.5.1  | 1 7                                                           |          |

|        | 5.1.1 Caltech's Design Methodology<br>5.1.2 Tangram and Balsa |          |

| 2.5.2  |                                                               |          |

| 2.5.3  | 1 1                                                           |          |

| 2.6    | Linear and Non-Linear Asynchronous Pipelines                  | 25       |

| 2.6.1  |                                                               | 26       |

| 2.6.2  | 1 0                                                           |          |

| 2.6.3  | J I                                                           |          |

| 2.6.4  | 1                                                             |          |

| 3. N   | New High Speed QDI Asynchronous Pipelines                     | 36       |

| 3.1    | Caltech's QDI templates                                       | 36       |

| 3.1.1  | WCHB                                                          | 36       |

| 3.1.2  |                                                               |          |

| 5.1.3  | 3 Why Input Completion Sensing?                               | 40       |

| 3.2   | New QDI Templates                              | 41 |

|-------|------------------------------------------------|----|

| 3.2.1 |                                                |    |

| 3.2.2 | 2 RSPCFB                                       | 50 |

| 3.2.3 | 3 FSM Design                                   | 53 |

| 3.2.4 |                                                |    |

| 3.2.5 | 5 Conclusions                                  | 58 |

| 4. T  | 'imed Pipelines                                | 59 |

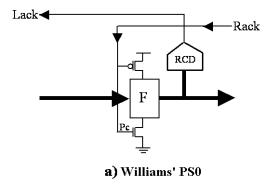

| 4.1   | Williams' PS0 Pipeline                         | 60 |

| 4.2   | Lookahead Pipelines (Single Rail)              | 62 |

| 4.3   | Lookahead Pipelines (Dual Rail)                | 65 |

| 4.4   | High Capacity Pipelines (Single Rail)          | 65 |

| 4.5   | Designing Non-linear Pipeline Structures       | 66 |

| 4.5.1 | 1 Slow and Stalled Right Environments in Forks | 67 |

| 4.5.2 | 2 Slow and Stalled Left Environments in Joins  | 68 |

| 4.6   | Lookahead Pipelines (Single Rail)              | 69 |

| 4.6.1 |                                                |    |

| 4.6.2 | , , , , , , , , , , , , , , , , , , ,          |    |

| 4.6.3 | 1 ,                                            |    |

| 4.7   | 1 /                                            |    |

| 4.7.1 | J                                              |    |

| 4.7.2 |                                                |    |

| 4.8   | High Capacity Pipelines (Single Rail)          |    |

| 4.8.1 | $\sigma$                                       |    |

| 4.8.2 | 1                                              |    |

| 4.9   | Conditionals                                   |    |

| 4.10  | Simulation Results                             |    |

| 4.11  | Conclusions                                    | 84 |

| 5. A  | Design Example: The Fano Algorithm             | 85 |

| 5.1   | The Fano Algorithm                             | 85 |

| 5.1.3 | 1 Background on the Algorithm                  | 85 |

| 5.2   | The Synchronous Design                         | 87 |

| 5.2.3 | Normalization and its benefits                 | 87 |

| 5.2.2 | 0                                              |    |

| 5.2.3 | 3 Chip Implementation                          | 93 |

| 6. T  | he Asynchronous Fano                           | 95 |

| 6.1   | The Asynchronous Fano Architecture             | 96 |

| 6.2   | The Skip-Ahead Unit                            |    |

| 6.3   | The Memory Design                              |    |

| 6.4   | The Fast Data and Decision Registers           |    |

| 6.5  | Simulation Results and Comparison             | 103   |

|------|-----------------------------------------------|-------|

| 7. A | An Asynchronous Semi-Custom Physical Design   |       |

| Flow | <i>T</i>                                      | .106  |

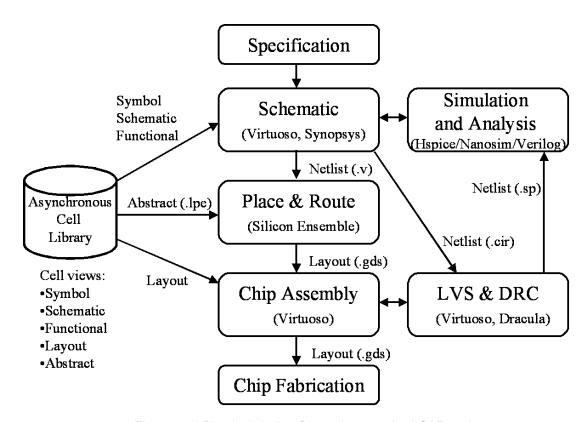

| 7.1  | Physical Design Flow Using Standard CAD Tools | 106   |

| 8. R | References                                    | . 116 |

# List Of Tables

Table 4.1: Cycle time (ns) of original linear pipelines vs. proposed non-linear pipelines ... 82

# **List Of Figures**

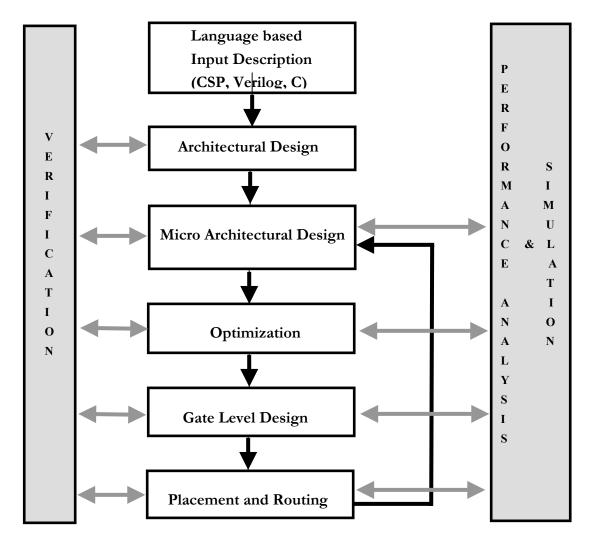

| Figure 1-1: Asynchronous circuit design flow under development                       | 8        |

|--------------------------------------------------------------------------------------|----------|

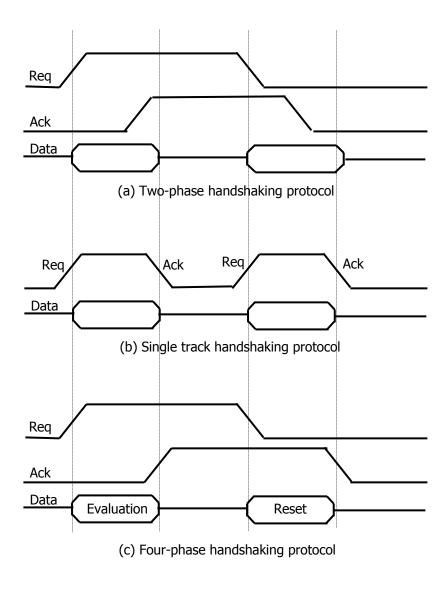

| Figure 2-1: Handshaking protocols: Two-phase versus four-phase                       | 14       |

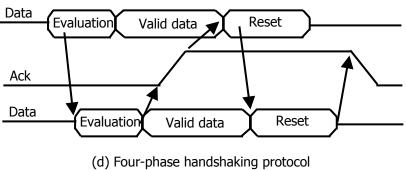

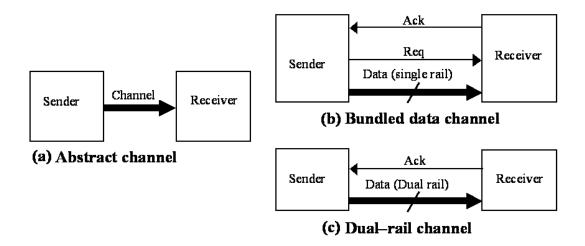

| Figure 2-2: Pipeline channels                                                        | 27       |

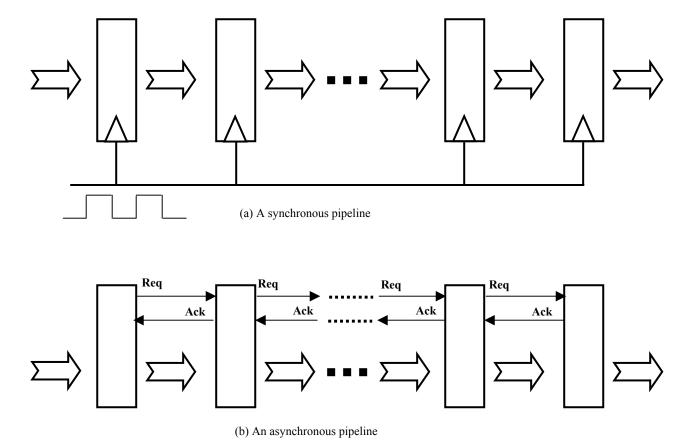

| Figure 2-3: Synchronous vs. asynchronous pipelines                                   | 28       |

| Figure 2-4: Throughput vs. tokens graphs                                             | 32       |

| Figure 2-5: a) a fork and b) a join                                                  | 34       |

| Figure 2-6: Fundamental non-linear pipeline structures                               | 35       |

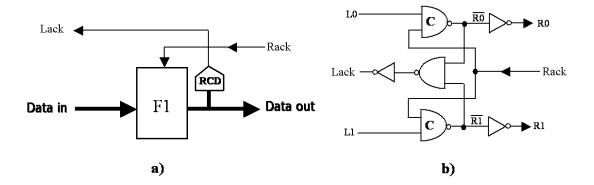

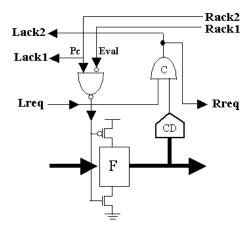

| Figure 3-1: WCHB                                                                     | 37       |

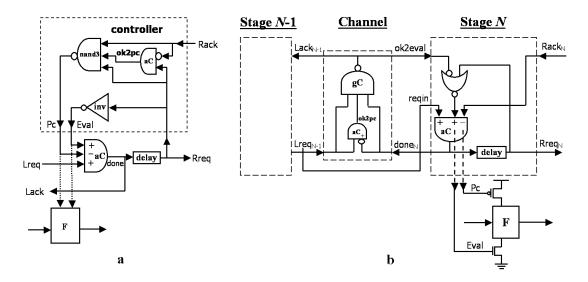

| Figure 3-2: a) PCHB and b) PCFB templates                                            | 38       |

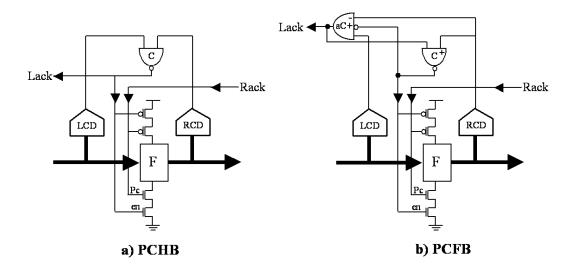

| Figure 3-3: a) PCHB and b) PCFB STG                                                  | 38       |

| Figure 3-4: An OR gate implementation using weak conditioned logic                   | 41       |

| Figure 3-5: Optimized PCHB for a 1-of-N+1 channel                                    | 42       |

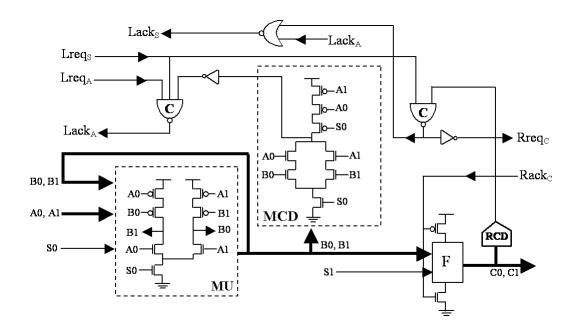

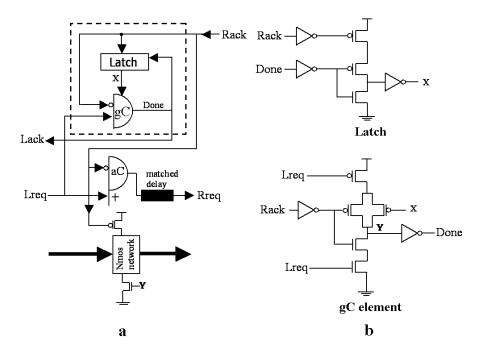

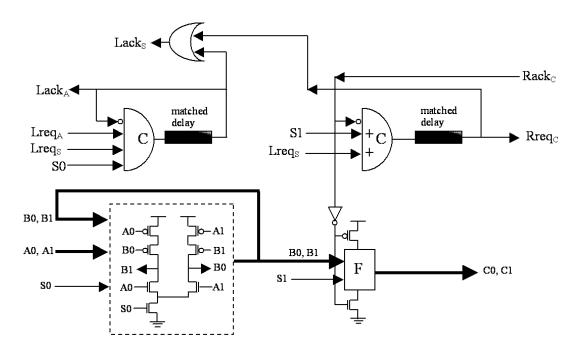

| Figure 3-6: a) Abstract and b) detailed QDI RSPCHB pipeline template                 | 44       |

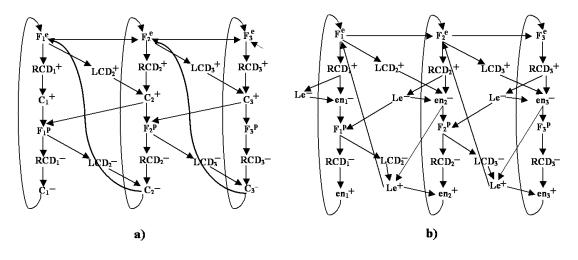

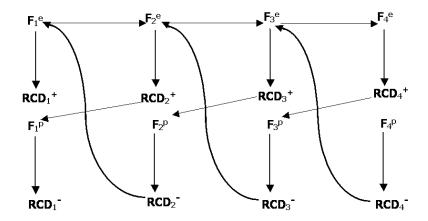

| Figure 3-7: The STG of the RSPCHB                                                    | 45       |

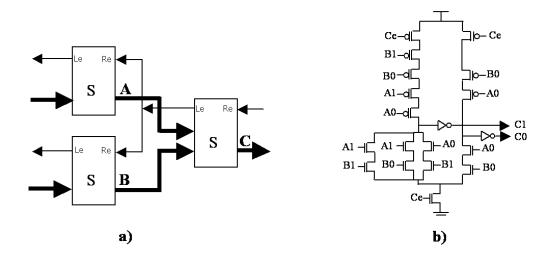

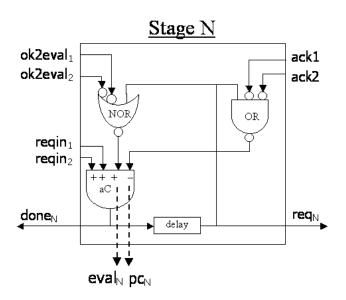

| Figure 3-8: Conditional a) join and b) split using RSPCHB                            | 47       |

| Figure 3-9: A RSPCHB 1-bit memory                                                    | 50       |

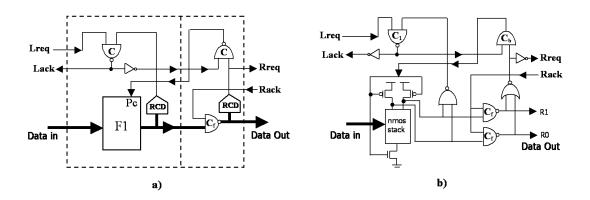

| Figure 3-10: a) Abstract and b) detailed RSPCFB                                      | 52       |

| Figure 3-11: a) Abstract and b) detailed RSPCFB                                      | 53       |

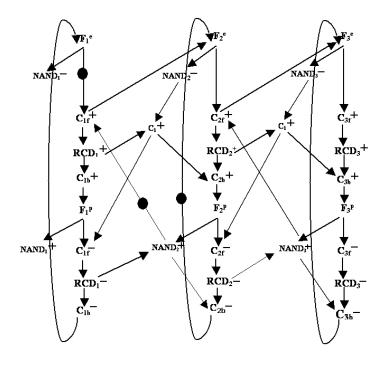

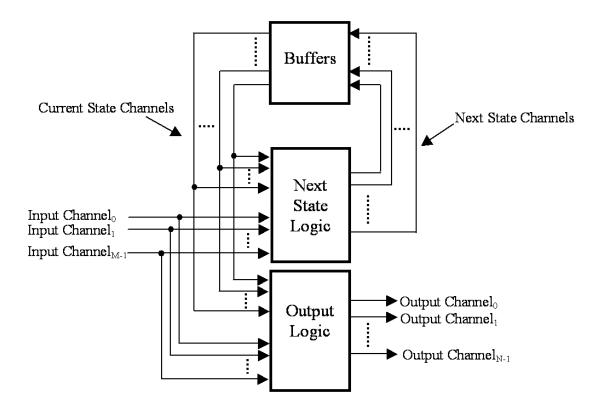

| Figure 3-12: An abstract asynchronous FSM                                            | 54       |

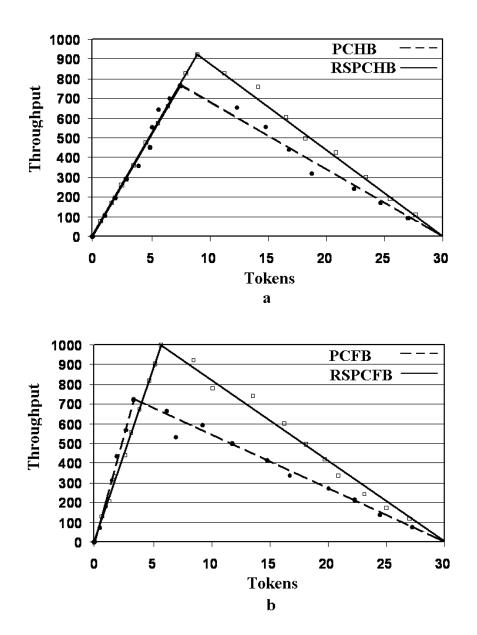

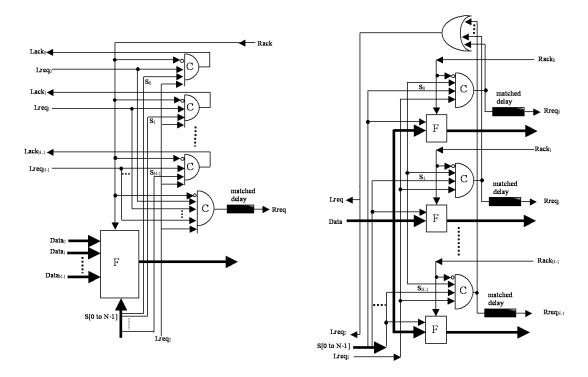

| Figure 3-13: Throughput versus tokens for a) the PCHB and RSPCHB and b) the PCFB and | d RSPCFB |

| linear pipelines                                                                     | 57       |

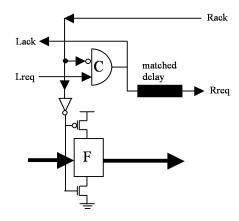

| Figure 4-1: Williams' PS0 pipeline stage                                             | 60       |

| Figure 4-2: The STG of the PS0 Pipeline                                                    | 62       |

|--------------------------------------------------------------------------------------------|----------|

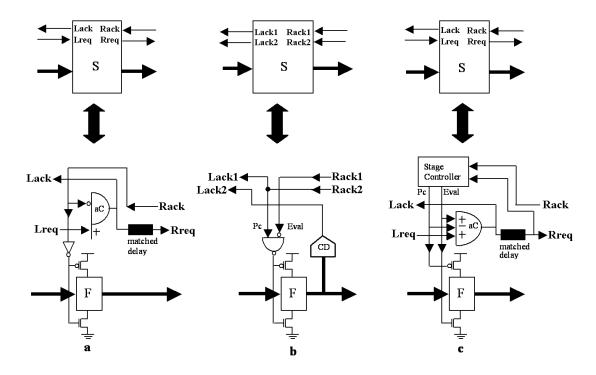

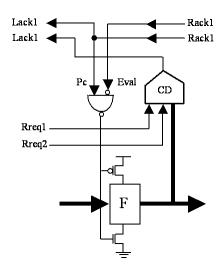

| Figure 4-3: a) LP <sub>SR</sub> 2/2 b) LP3/1 and c) HC pipelines                           | 64       |

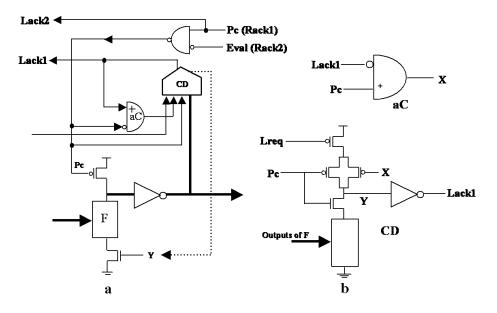

| Figure 4-4: a) Modified first stage after the fork. b) Detailed implementation of the gate | s in the |

| dotted box                                                                                 | 71       |

| Figure 4-5: The LP <sub>SR</sub> 2/2 pipeline stage with a symmetric c-element             | 72       |

| Figure 4-6: The LP3/1 pipeline with a modified CD to handle joins                          | 74       |

| Figure 4-7: a) Modified first stage after the fork. b) Detailed implementation of the ac   | ditional |

| gates                                                                                      | 74       |

| Figure 4-8: The LP3/1 stage with a C-element                                               | 75       |

| Figure 4-9: a) Original and b) New HC stage                                                | 77       |

| Figure 4-10: A 2-way join 2-way fork HC stage                                              | 78       |

| Figure 4-11: Conditional read and b) write.                                                | 80       |

| Figure 4-12:A one-bit LP <sub>SR</sub> 2/2 memory                                          | 81       |

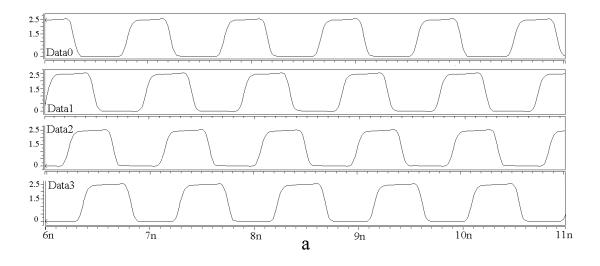

| Figure 4-13: HSPICE Waveforms. a) Linear pipeline, b) Two-way fork and c) Two-way jo       | oin 83   |

| Figure 5-1: Flow-chart of Fano Algorithm                                                   | 87       |

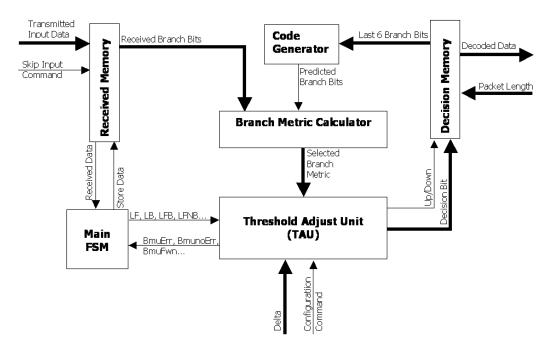

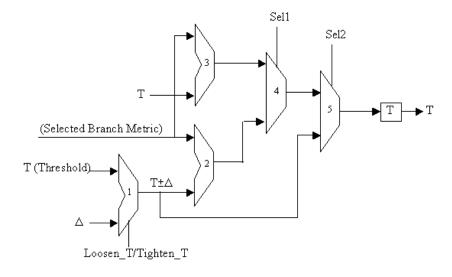

| Figure 5-2: RTL architecture of the synchronous Fano Algorithm                             | 90       |

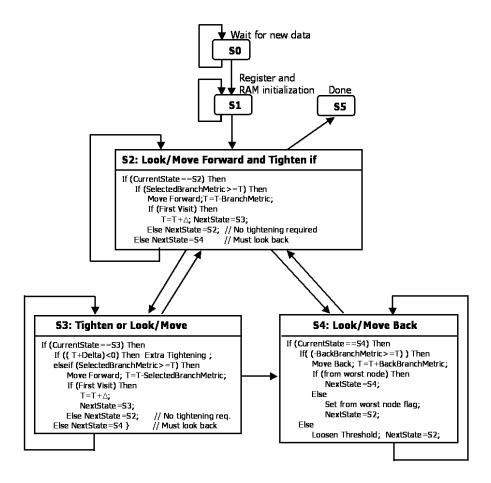

| Figure 5-3: Finite State Machine describing the RTL                                        | 92       |

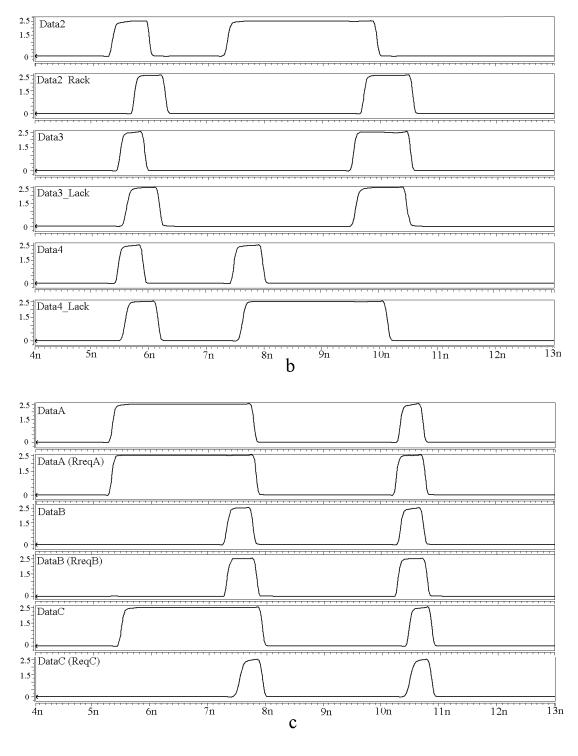

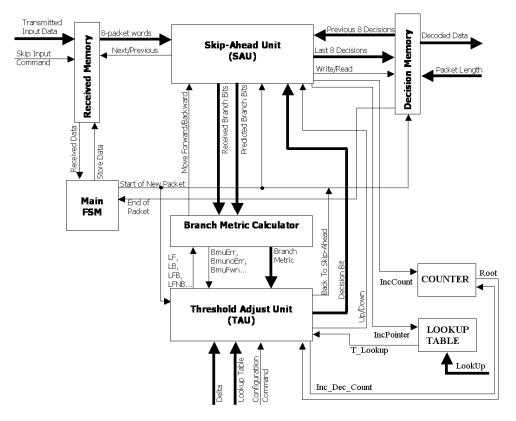

| Figure 6-1: RTL architecture of the asynchronous implementation                            | 97       |

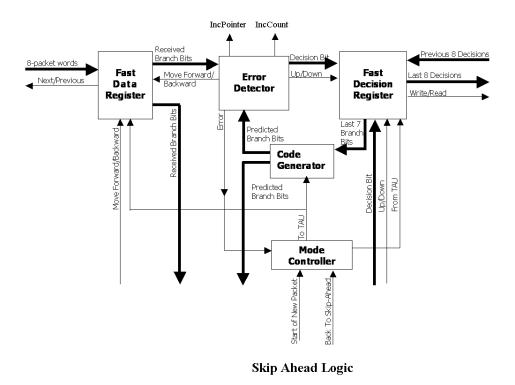

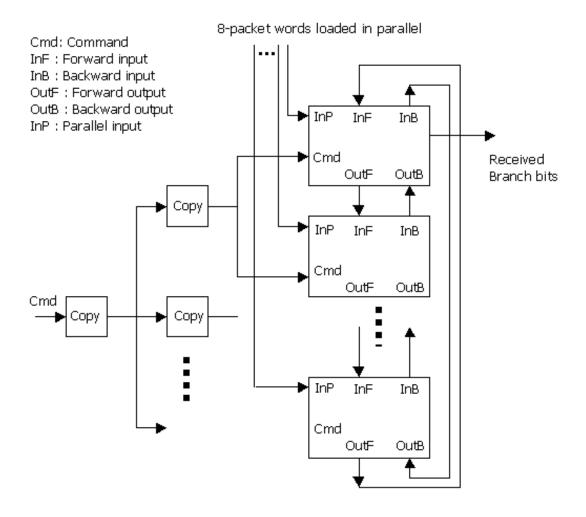

| Figure 6-2: Detailed implementation of the Skip-Ahead Unit                                 | 99       |

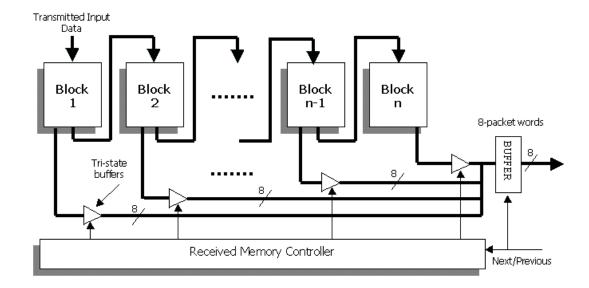

| Figure 6-3 Implementation of the Received Memory                                           | 101      |

| Figure 6-4 Implementation of a 1-bit fast shift register                                   | 103      |

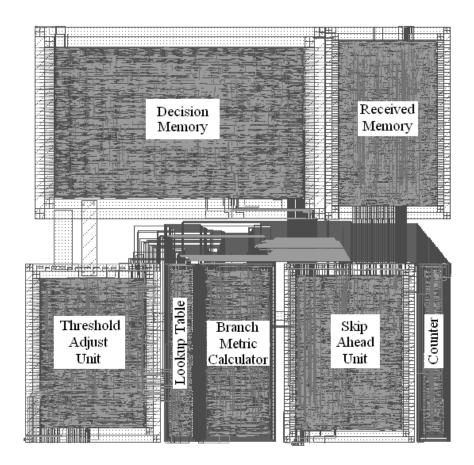

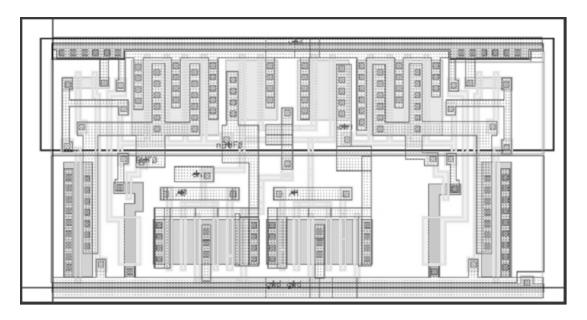

| Figure 6-5: Layout of the asynchronous Fano                                                | 104      |

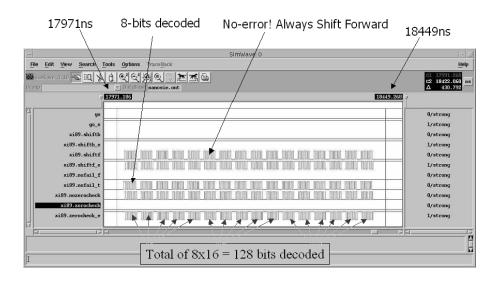

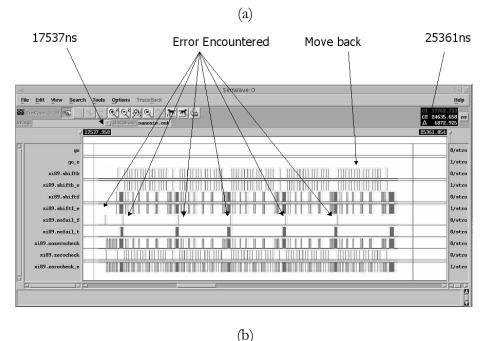

| Figure 6-6: a) Error-Free and b) Error Region operation waveforms                          | 105      |

| Figure 7-1: Physical design flow using standard CAD tools                                  | 107      |

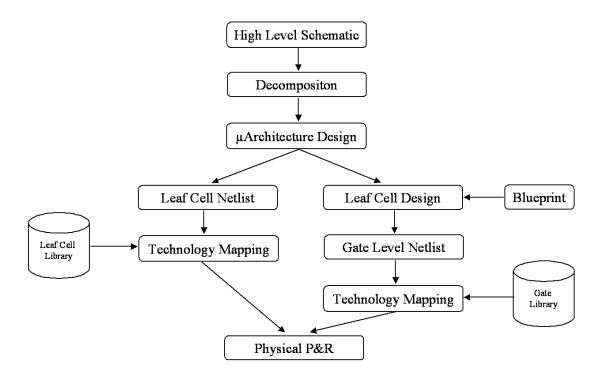

| Figure 7-2: Asynchronous circuit design flow followed      | . 108 |

|------------------------------------------------------------|-------|

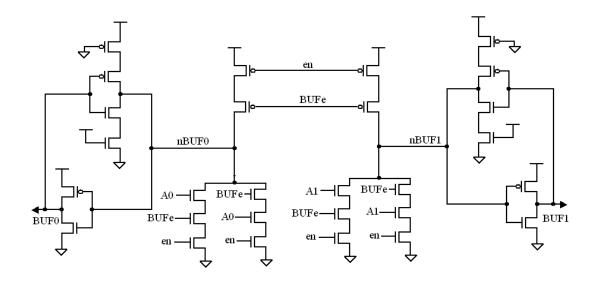

| Figure 7-3: The functional description of a dynamic buffer | . 110 |

| Figure 7-4: The transistor view of a dynamic buffer        | . 111 |

| Figure 7-5: The layout view of a dynamic buffer            | . 111 |

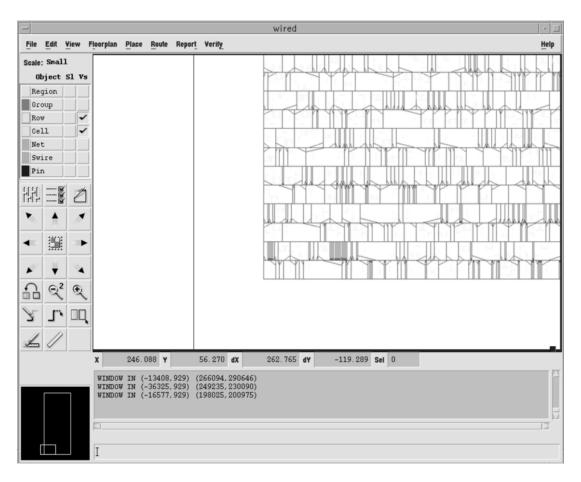

| Figure 7-6: Cell placement in Silicon Ensemble             | . 113 |

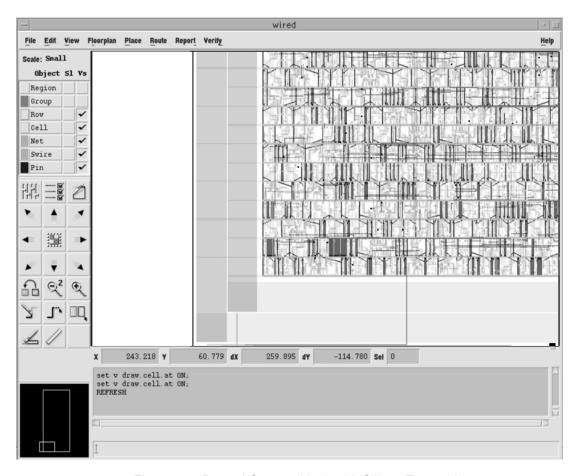

| Figure 7-7: Routed Counter block with Silicon Ensemble     | . 114 |

| Figure 7-8: Extracted netlist of a block                   | . 115 |

## **Abstract**

Asynchronous design is increasingly becoming an attractive alternative to synchronous design because of its potential for high-speed, low-power, reduced electromagnetic interference, and faster time to market. To support these design efforts, numerous design styles and supporting CAD tools have been proposed. We adopt a template-based methodology that facilitates hierarchical design using standard asynchronous channel protocols, removes the need for complicated hazard-free logic synthesis, and naturally provides fine-grain pipelines with high throughput. We propose seven different templates that provide tradeoffs between throughput and robustness to timing. The most robust templates are quasi-delay-insensitive in that they work correctly regardless of delays on individual gates. The most aggressive templates use timing assumptions that can be satisfied with additional care during transistor sizing, floorplanning, and layout.

We propose a complete design methodology for template-based designs using standard hardware description languages and the Cadence design framework. We demonstrate the advantages of the templates and methodology by designing an asynchronous sequential channel decoder based on the Fano algorithm. Spice simulations, on the extracted layout, show that the circuit runs at 450MHz and consumes 32mW at 25°C. The asynchronous chip runs about 2.15 faster and consumes 1/3 the power of its synchronous counterpart.

# Chapter 1

## 1. Introduction

Digital VLSI circuit design styles can be mainly classified as either synchronous, asynchronous or some mixture. Synchronous designs, consists of subsystems, which are controlled by one or more clocks that control synchronization and communication between blocks, have dominated the design space since the 1960's. Combinational logic is placed in between clocked registers that hold the data. The delay through the combinational logic plus relevant setup time should be smaller than the clock cycle time. In fact, the data at the inputs of the registers may exhibit glitches or hazards as long as they are guaranteed to settle before the sample clock edge arrives. Asynchronous methodologies, in contrast, use event-based handshaking to control synchronization and communication between blocks. This chapter first reviews various synchronous design methodologies and then describes some potential advantages of asynchronous design, before providing a more detailed overview of the thesis.

Synchronous design methodologies can be classified in one of two main categories; standard cell design and full custom design. Semi-custom standard-cell-based design methodologies offer good performance with typically 12-month design times [1]. They are supported by a large array of mature CAD tools that range from simulation, synthesis, verification, and test. The synthesis task is divided into architecture definition, logic/gate-level design, and physical design.

A large library of standard-cell components that have carefully been designed, verified,

and characterized supports the synthesis task. This library is generally limited to static CMOS based gates for a variety of reasons. Compared to more advanced dynamic logic families, standard CMOS static logic has higher noise margin and thus requires far less analog verification, significantly reducing design time.

Standard-cell designs also use standard clocking strategies to facilitate more automation and reduced design times. The forms of gated clocking are limited, reducing power efficiency. Standard flip-flop based designs are used to simplify timing analysis despite the incurrence of significant data to clock output overheads.

Moreover, the time-to-market advantage of standard-cell based designs is being attacked by the increasingly difficult task of estimating wire-delay. In submicron designs, the process of architecture, logic, and technology mapping design could proceed somewhat independently from placement and routing of the cells, power grid, and the clocks because wire-delays were negligible compared to gate-delays. In deep-submicron design, however, the relative delay of long-range wires are increasing and becoming harder to estimate. This is causing the traditional separation of logic synthesis and physical design tasks to break down because synthesis is not properly accounting for actual wire delays. This timing-closure problem has forced numerous shipment schedules to slip. EDA vendors have now developed a new suite of emerging CAD tools that address aspects of the physical design must occur much earlier in the design process.

In the future, predictions suggest that long-range wires may have 5 to 20 clock cycles in delay making estimation particularly critical [1]. In particular it is predicted that that high-speed clock regions communicating at perhaps reduced frequencies may become prevalent, but the semi-custom CAD support for multiple clock domains is just emerging. The

simplest approach involves adding synchronizers between clock domains that incurs a significant latency penalty.

Some manufacturers have extended the standard cell design technique to the design of datapaths and other higher-level functions such as microprocessors and their peripherals. On the other hand the design can also be implemented by optimizing every transistor of the layout. This technique is called full custom design, and is generally preferred when one or many aspects of the chip need to be optimized beyond what is readily available in a semi-custom approach. Since the designer controls the transistor size, placement of the smallest functional blocks and the main routing method, the end result in general is much better than standard cell design. In the full custom method, design time is traded in for higher performance, reduced area or power consumption, since all possible circuit techniques can be applied, where as in standard cell design, the CAD tool only has a limited number of pre-laid out cells that need to be broad enough to suit every customers need.

Full-custom design houses have found that these challenges with standard cell design can be overcome with longer design cycles of an average of 36 months. In particular, the use of advanced logic dynamic logic styles has been an area of growing interest in full-custom designs [2] [3] [4] [5]. Domino logic is estimated to be 30% faster than static logic because of the improving logical effort derived by the removal of PMOS logic. Traditional domino logic however still suffers from overhead associated with clock skew and latch delays. More advanced flip-flops and latches have been developed that somewhat improve the clock skew overhead and reduce the latch delays. At the extreme, the latch delays can be removed using multiple overlapping clocks in a widely used technique, recently named skew-tolerant domino logic [5].

In addition to the problems of clock distribution and skew is the problem of heat and power consumption. Many of the gates switch because they are connected to the clock, not because they have new input data to evaluate. The biggest gate of all is the clock driver, and it must switch all the time to provide the correct timing, even if only a small part of the chip has anything useful to do. Although gating the clock is an option to send the clock signal to only those who need it, stopping and starting a high-speed clock is not easy.

To reduce power consumption, particularly in memories and long-distance on-ship and off-chip communication, low-voltage signalling has been commonly used. These also suffer from reduced noise margins, requiring more manual design practices and extensive analog simulation.

The basic cost that achieving this higher performance and low-power presents is the reduced noise margin and the increased need for more careful, manual design practices and extensive analog verification, pre and post layout.

The increasing limitations and growing complexity of both standard-cell and full-custom synchronous design have led to a change of focus on digital circuit design. In particular, circuits that lack a global controlling clock, namely asynchronous circuits have demonstrated potential benefits in many aspects of system design (e.g. [6], [7], [8], [9], [10], [11], [12], [13], [14]). Asynchronous circuits have several advantages over their synchronous counterparts, including:

1) Elimination of clock skew: Clock skew is defined as the arrival time difference of the clock signal to different parts of the circuit. In general in standard cell design, to avoid this problem, the clock pulse is increased to assure correct operation, which yields slower running circuits. However in full custom design buffer insertion, or careful clock tree

design and analysis to improve clock routing and clock power are some of the methods synchronous designers are using to handle this problem. Although full custom design approach leads to reduction or even elimination of clock skew, for synchronous design this is still a problem that needs to be worked on. On the other hand, since asynchronous circuits have no global clock that controls the data flow, there is no clock skew problem.

- 2) Lower power consumption: In general, the constant activity of the clock signal causes synchronous systems to consume power even though some parts of the circuit may not be processing any data. Even though some improvements in full custom design, such as clock gating avoid sending the clock signal to the un-active parts the clock driver has to constantly provide a powerful clock to able to reach all the parts of the circuit. Although asynchronous circuits in general have more transitions due to the hardware overhead, they generally have transitions only in areas that are active in the current computation.

- 3) Average case performance: Synchronous circuit designers have to consider the worst-case scenario when setting the clock speed to ensure that all the data has stabilized to before being latched. However asynchronous circuits detect and react when the computation is completed, yielding average case performance rather than worst case [14].

- 4) Easing of global timing issues: since in synchronous circuits the slowest path dictates the clock speed, designers try to optimize all the paths to achieve the highest possible clock rate. In particular there maybe long wires, which require large buffers and consume significant power even though they may be non-critical or maybe infrequently driven. In contrast in asynchronous circuits optimizing the frequently used paths is easier [9].

- 5) Better technology migration potential: Since the technology which the circuit is implemented improves rapidly, for synchronous circuits better performance often can only

be achieved by migrating all the system components to the new technology where as for asynchronous design the communication between blocks only occur when the completion of the processing is detected, therefore different delays introduced with different technologies can be easily substituted into a system without altering other structures.

- 6) Automatic adaptation to physical properties: The delay on a path may change to the variations in the fabrication process, temperature, and power supply voltage. Synchronous system designers must consider the worst case and set the clock period accordingly. However asynchronous circuits naturally adapt to changing conditions since the slowdown on any path does not affect the functionality of the system [15].

- 7) Improved EMI: In a synchronous design, all activity is locked into a very precise frequency. The result is nearly all the energy is concentrated in very narrow spectral bands at the clock frequency and its harmonics. Therefore, there is substantial electrical noise at these frequencies. Activity in an asynchronous circuit is uncorrelated, resulting in a more distributed noise spectrum and a lower peak noise value [16].

# 1.1 Asynchronous Circuit Design Flow

The USC Asynchronous CAD and VLSI group, jointly with the Columbia Asynchronous group, is currently developing a complete asynchronous circuit design methodology that will support automated design exploration of both high-performance and low-power asynchronous circuits. The basic steps of the methodology are illustrated in Figure 1.1. First a language based, model such as CSP [17] and Verilog [18], is used as the input description. This input description describes the desired top-level functionality of the chip and maybe annotated with overall constraints on power, energy consumption, throughput, latency, chip area, etc. Note that details regarding internal structure or the

specific asynchronous protocols used are specifically not included in the description. After generating this input description and verifying its correctness, the next step in the methodology is to explore and finalize a basic architecture for the design. This basic architecture should identify the number and relative characteristics of the basic blocks in the design (register files, ALUs, multipliers, etc.) To automate this step we expect to adapt variations in classical high-level synthesis, i.e., scheduling, resource sharing, and binding. After architectural design is complete, the next step in the methodology is micro-architecture design. In this step the designer can choose to implement the architecture with various methods ranging from fine grain pipelines template-based using delay insensitive cells to components relying on bounded delay based with no pipelining at all. Depending on the style chosen, various optimizations can be applied, namely selection of the handshaking protocol, defining the level of pipelining, and slack optimization for pipelined designs. Once this initial mirco-architecture is created, next step is to identify critical components and perform handshaking optimization to achieve higher performance and lower power. Based on the final micro-architecture, a gate or transistor level design is generated. This can be done either automatically using new template-based synthesis techniques that our group is creating or manually.

Figure 1-1: Asynchronous circuit design flow under development

Finally, placement and routing will be applied very a similarly to that required synchronous circuit design. In every step all the design process, verification and performance analysis tools are used to verify correct functionality and overall performance. The focus this proposal is the generation of new templates for template-based design, as well as to help develop the above CAD frame for the automated design of asynchronous systems.

## 1.2 Expected Contributions of the Thesis

Our research group's goal is to produce a complete design method for asynchronous systems, including specification, synthesis, verification, simulation, and testing and to develop a suite of CAD tools supporting the design method. And by using these CAD tools to design high-performance and energy-efficient asynchronous microprocessors, and systems-on-a-chip. As part of an ongoing research to accomplish these goals the we:

- Develop two new quasi delay insensitive, high-speed templates targeted at non-linear pipelines, which are faster and smaller than other quasi delay insensitive templates. Quasi delay insensitive templates are the most robust asynchronous building blocks for designs based on templates. By using templates we can mimic ease of design of the standard cell design methodology in synchronous design. We also show the implementation of some of the non-linear structures.

- To achieve higher speeds, we then develop five new bounded delay pipeline templates by modifying and further improving the templates developed by Columbia University, which are based on timing assumptions to shorten handshaking time and achieve higher speeds. In particular, the templates developed by Columbia University were targeted for linear pipelines such as FIFOs. Real life designs however, require more complex structures that require the template to also function correctly with non-linear pipelines. To extend the existing pipelines we modify each template to handle non-linear pipelines with little impact on performance.

- We then implement a communication algorithm as a design example in both synchronous and asynchronous methods to show the advantages of asynchronous

design over synchronous design as well as to help the development of a CAD environment, which is mainly targeted for template, based design. The asynchronous implementation of the algorithm will also be used to study the trade offs among different asynchronous templates from timed to delay insensitive.

# 1.3 Thesis Organization

The organization of the reminder of this proposal is as follows. Chapter 2 presents background on asynchronous circuit design styles, and linear and non-linear pipeline applications, Chapter 3 presents the new high speed QDI pipelines, Chapter 4 presents the extension to the pipelines introduced by Columbia University and the introduction of five new timed templates, Chapter 5 presents the design example in synchronous, and Chapter 6 presents in asynchronous. Finally, Chapter 7 presents our semi-custom asynchronous design flow.

# Chapter 2

# 2. Background

This section presents the basics of asynchronous circuit design and classifies many of the existing asynchronous circuit design styles according to data encoding method, handshaking style, granularity of pipelines and circuit style. Then we describe the differences between logic synthesis-based methodologies and those that rely more on a template-based methodology. We then focus on existing templates that support the design of complex fine-grain pipelines and analyze their performance.

## 2.1 Data Encoding Styles

Single rail [19] communication between functional blocks consists of one request wire and one wire per data bit from the sender to the receiver and one acknowledgment wire from the receiver to the sender. Dual rail communication often consists of two wires per data bit from the sender to the receiver and one acknowledgment wire from the receiver to the sender. In addition, dual-rail designs can have an additional request line [20]. 1-of-N communication is a generalization of dual rail communication in which [log<sub>2</sub>N] bits are sent using N wires.

An acknowledgment signal from the receiver to the sender is used to tell the sender that the data is no longer needed. The logic that drives this acknowledgment signal often involves *completion sensing circuitry* that helps determine when the receiver is done using the current data bits. In single rail communication, completion sensing circuits are implemented with *bundled data* lines [19] or more sophisticated speculative completion sensing circuitry [21], [22], that includes delay lines that match the critical paths of the

functional unit. On the other hand, completion sensing of dual rail designs can be done using specialized logic that actively identifies when the computation is done. This latter logic relies on the dual-rail nature of the data and can be implemented without relying on timing assumptions and thus, is more robust to variations in delay than its delay-line counterparts. Completion sensing, however, requires more circuitry than delay lines and, if not done wisely, can incur a significant performance, power and area penalty.

The functional units can be implemented using static or dynamic logic. Often functional units that communicate using dual rail or 1-of-N styles are implemented using dual rail dynamic logic [23] [24], but since static logic is also possible [23]. Functional units that communicate using single rail are more commonly implemented using static logic that is often smaller and consumes less power than dynamic counterparts. Designs implemented with dynamic logic, however, can generally achieve higher throughput than their static logic counterparts. Consequently, they can run at lower voltages to achieve a given throughput requirement and, thus may yield a lower power design than their single rail counterparts.

# 2.2 Handshaking Styles

Asynchronous circuits consist of functional units that communicate control and data information using various handshaking styles. The most dominant forms of handshaking styles two-phase [25] and four-phase handshaking [26] are shown in Figure 2.1. In two-phase handshake protocol, a request and an acknowledge wire is used to implement handshaking between the sender and the receiver. In two-phase handshake protocol, all transitions are functional and consequently every pair of consecutive request/acknowledge transitions forms a complete handshake. Two-phase single rail communication is usually seen with static logic functional units that use bundled-data for completion sensing. Due to some

difficulties in designing complex two-phase control circuits, a novel single-track handshaking protocol has been suggested by van Berkel and Bink [27]. This handshaking protocol is achieved by combining the request and acknowledge lines into one wire and is illustrated in Figure 2.1 (b). Where two-phase handshaking involves two events per cycle, four-phase handshaking requires four events, as shown in Figure 2.1 (c). Since four events are used to designate a complete handshaking cycle, half of these are essential for functional computation and the other half are not actively used to communicate data. Nevertheless, this reset phase is very useful for precharging dynamic units. Figure 2.1 (d) shows a four-phase handshaking protocol for dual-rail dynamic units [23] [24]. Other protocols extend the data valid region through the reset phase [19] [28], to more efficiently use four-phase handshaking with static functional units.

Figure 2-1: Handshaking protocols: Two-phase versus four-phase.

## 2.3 Delay Models

Most design techniques require some timing assumptions or constraints on the wires and/or components to ensure correct operation. For example, in synchronous circuit design, the data input to every register must satisfy all setup and hold times. The delay assumptions in asynchronous circuits widely vary based on design styles as outlined below.

- Delay insensitive (DI): Delay insensitive designs [29] [30], require no timing assumptions on wither wires or gates. That is, DI circuits work correctly for any arbitrary, time-varying gate and wire delay. This is the most conservative and robust design style, but it has been shown that very few gate-level delay insensitive designs can exist [31]. That said, delay insensitivity can more easily and practically be achieved at a block level where blocks communicate only through delay insensitive channels.

- Quasi delay insensitive (QDI): Quasi delay insensitive design [32] [24] is a practical approximation to delay insensitive design. QDI circuits work correctly regardless of delays in gates and all wires except in cases of wire forks designated *isochronic*. The difference in time at which the signal arrives at the ends of an isochronic fork must be less than the minimum gate delay. If these isochronic forks are guaranteed to be local to a small component, these circuits can be practically as robust as DI circuits. The QDI assumption has also been extended to include assumptions of isochronic propagation through a number of logic gates [33].

- Speed independent (SI): SI design [23] [34], assumes that gate delay can be arbitrary but

that all wire delay is negligible. From a delay perspective SI design basically assumes that all forks are isochronic. For the design of small control circuits, thus timing assumption is generally satisfied.

- Scalable delay insensitive (SDI): SDI approaches [36] [21], are motivated by the observation that SI design should not be used for any circuit that spans significant chip area. Consequently, in SDI design the chip area is divided into many regions, SI circuit design is used within each region, and communication between regions is done delay insensitively.

- Bounded delay: In bounded delay models each gate is given a minimum and maximum delay and the circuit must work if the delay of all gates are within these bounds. These timed circuits can often be faster, smaller and lower power than their QDI or SI counterparts, but require more careful timing verification during physical design [37].

- Relative timing: In relative timing based circuits, a list of relative orderings of events identifies sets of path pairs, where for each pair of paths, one path must be longer/shorter than each other to ensure correctness. These circuits can have the same benefits of times circuits and may be easier to validate [38] [39] [40].

# 2.4 Synthesis Based Design

#### 2.4.1 Fundamental Mode Huffman Circuits

In this model, the circuit design flow is similar to that of the design of synchronous circuits[15]. The circuit is usually expressed as a *flow table* [41]. The flow table has a row for each internal state, and a column for each combination of inputs. The entries indicate the

next state entered and output generated when the column's input combination is seen while in the row's state. States where the next state is identical to the current state are called *stable states*. It is assumed that each unstable state leads directly to a stable state, with at most one transition occurring on each output variable. Similar to finite state machine synthesis in synchronous systems, state reduction and state encoding is performed on the flow table, and Karnaugh maps generated for each of the resulting signals.

There are several points that need to be considered for this design method. The system responds to input changes rather than clock ticks therefore the circuit may enter some intermediate states if multiple inputs change at the same time. Therefore it must be guaranteed that these intermediate states should still lead to the intended stable state, irrespective of the order of how inputs change.

Another concern is hazard removal. Since hazards, static or dynamic, can cause the circuit to enter an unstable state, they must be eliminated by adding a sum-of-products circuit that has functionally redundant products.

Due to the restriction of only one input changing to the combinational logic at a time, several requirement need to be forced on the implementation of sequential circuits. First, the combinational logic must settle in response to a new input before the present state entries change. The state encoding must assure a single bit transition for state transitions. The last requirement is that the next external input transition cannot occur until the entire system settles to a stable state.

While the fundamental mode assumption makes logic design easy, it also increases cycle time. There are proposed solutions, which carefully analyze an implementation to relax the fundamental mode assumption, however because of the limitations on the multiple input changes, this design methodology has never achieved wide acceptance for complex system design. Burst-mode circuits, covered in the next section, overcome the limitations on multiple input changes.

### 2.4.2 Burst-Mode Circuits

The *burst-mode* design style developed by [42], [43], [44] is based on the earlier work at HP laboratories by [45], attempts to move even closer to synchronous design than the Huffman method [15]. In this method, circuits are specified via a standard state-machine, where each arc is labeled by a non-empty set of inputs (an *input burst*) and a set of outputs (an *output burst*). The assumption is that, in a given state, only the specified inputs on one of the input bursts leaving that state can occur. The inputs are allowed to occur in any order. The state reacts to the inputs only when all of the expected inputs have occurred. The state machine then fires the specified output bursts and enters the specified next state. New inputs are only allowed to occur after the system has completely reacted to the previous input burst. Therefore, the burst-mode method still requires the fundamental-mode assumption, but only between transitions in different input bursts. Another restriction is that no input burst can be a subset in another input burst leaving the same state.

Burst-mode circuits can be implemented in various ways, including similar techniques to those of Huffman circuits.

The problems with both the fundamental-mode and burst-mode circuits that restrict these circuits are the fact that circuits often are not simple single gate small state machines, but instead complex systems with multiple control state machines and datapath elements. These methods do not discuss system decomposition for complex circuits. Also, these methodologies cannot design datapath elements. This is because datapath elements tend to

have multiple input signals changing in parallel, and the fundamental-mode assumption would be easily violated. Although one solution for datapath implementation is to use synchronous components with careful add-hoc optimization, another issue is the increased delay by the additional delay elements to satisfy the fundamental-mode assumption. Not only is the delay increased but it must also be able to work under worst-case scenario.

### 2.4.3 Event-Based Design

Petri nets and other graphical notations are a widely used alternative to specify and synthesize asynchronous circuits. In this model, an asynchronous system is viewed not as state-based, but rather as a partially ordered sequence of events. A Petri net [46] is a directed bipartite graph, which can describe both concurrency and choice. The net consists of two kinds of vertices: places and transitions. Tokens are assigned to the various places in the net. An assignment of tokens is called a marking, which captures the state of the concurrent system. When all the conditions preceding a transition are true the action may fire which removes the tokens from the preceding places and marks the successor places. Hence, starting from an initial marking, tokens flow through the net, transforming the system from one marking to another. As tokens flow, they fire transitions in their path according to certain firing rules.

Patil proposed the synthesis of Petri nets into asynchronous logic arrays. In this approach, the structure of the Petri net is mapped directly into hardware. Many modern synthesis methods use a Petri net as a behavioral specification only, not as a structural specification. Using reachability analysis, the Petri net is typically transformed into a state graph, which describes the explicit sequencing behavior of the net. An asynchronous circuit is then derived from the state graph.

More general glasses of Petri nets include Molnar *et al.'s I-Nets* [47], and Chu's *Signal Transition Graphs* or *STGs* [48]. These nets allow both concurrency and a limited form of choice. Chu developed a synthesis method, which transforms an STG into a speed-independent circuit, and applied the method to a number of examples.

Petrify is a tool for manipulating concurrent specifications and synthesis and optimization of asynchronous control circuits [49]. Given a Petri net, or a STG it generates another Petri net or STG, which is simpler than the original description and produces an optimized net-list of an asynchronous controller in the target gate library while preserving the specified input-output behavior. An ability of back annotating to the specification level helps the designer to control the design process.

For transforming a specification petrify performs a token flow analysis of the initial Petri net and produces a transition system. In the initial transition system, all transitions with the same label are considered as one event. The transition system is then transformed and transitions relabeled to fulfill the conditions required to obtain a safe irredundant Petri net. For synthesis of an asynchronous circuit petrify performs state assignment by solving the *Complete State Coding* problem. State assignment is coupled with logic minimization and speed-independent technology mapping to a target library. The final netlist is guaranteed to be speed-independent, i.e., hazard-free under any distribution of gate delays and multiple input changes satisfying the initial specification. The tool has been used for synthesis of Petri nets and Petri nets composition, synthesis and re-synthesis of asynchronous controllers and can be also applied

# 2.5 Template-Based Design

A different approach is for asynchronous design is to view the system as

communication blocks or processes, called templates that encapsulate all the design constraints inside the modules. These templates will have requirements of their environment that must be met, and which will restrict how these templates are used. However, such restrictions or internal timing constraints are much simpler than those of most other methodologies, and the proper template will usually be obvious from the functionality required.

Template-based design is somewhat similar to standard cell design in synchronous logic.

Templates can be either pre-designed to implement simple logic functions, with handshaking, or can synthesized to create more complex ones.

The advantage of template-based design is the ease of manual design. In general a datapath is created, and the control unit is designed around the datapath. Once a general architecture is created the rest of the task is to implement the blocks of the architecture using templates. Also template-based design has the potential advantage, which is currently being investigated, of being able to be used as a backend to a synchronous CAD tool. The highly optimized synchronous design can be converted to an asynchronous one by replacing every gate with its asynchronous handshaking counterpart template. However additional optimization might be required to improve the performance of the system.

### 2.5.1 Template-Based Compilation Systems

Although template-based system can ease manual design, their main power is seen when they are coupled with a high-level language and automatic translation software. The following section presents some well-known methodologies, which have their own language for easy compilation of asynchronous systems.

#### 2.5.1.1 Caltech's Design Methodology

Caltech's communicating processes compilation technique [50], translates programs written in a language similar Communicating Sequential Processes into asynchronous circuits, which communicate on channels. The source language describes circuits by specifying the required sequences of communications in the circuit.

Caltech's translation process is accomplished in several steps: (1) in process decomposition, a process is refined into an equivalent collection of interacting simpler processes; (2) in handshaking expansion, each "communication channel" between processes is replaced by a pair of wires, and each atomic "communication action" is replaced by a handshaking protocol on the wires; (3) in production-rule expansion, each handshaking expansion is replaced by a set of "production rules (PRs)", where each rule has a "guard" that insures it is activated (i.e., "fires") under the same semantics as specified by the earlier handshaking expansion; and finally, (4) in operator reduction, PRs are grouped into clusters, and each cluster is than mapped to a basic hardware component. It is important to realize that many of these steps require subtle choices that may have significant impact on circuit area and delay. Although heuristics are provided for many of the choices, much of the effort is directed towards aiding a skilled designer instead of creating autonomous tools. This has the benefit in that the designer can usually make better decisions, provided that the designer is skilled enough.

Caltech has later moved to using more standardized, pre-designed, less complex building blocks, which simplify the design method, explained above. Caltech's template-based design methodology has moved from the synthesis of complex templates to chip implementation using smaller, and simpler templates, which have very standard design

guidelines. These templates are in general targeted for implementing fine grain pipelined chips.

#### 2.5.1.2 Tangram and Balsa

Another compiler-based approach developed by van Berkel, Rem and others [51], at Philips Research Laboratories and Eindhoven University of Technology uses the *Tangram* language. Tangram, which is based on CSP, is a specification language for concurrent systems. A system is specified by Tangram program, which is then compiled by syntax-directed translation into an intermediate representation called a *handshake circuit*. A handshake circuit consists of a network of *handshake processes*, or *components*, which communicate asynchronously using handshaking protocols. The circuit is then improved using peephole optimization and, finally components are mapped to VLSI implementations.

Although Tangram is also syntax derived like Caltech's design methodology, it also targets non-pipelined designs, which can support non-linear sequential processing as well as pipeline processing.

The Tangram compiler has been successfully used at Philips for several experimental DSP designs and electronics; including counter, decoders, image generators, and an error corrector for a digital compact cassette player.

Balsa [52], developed at University of Manchester, adopts syntax-directed compilation into handshaking components and closely follows Tangram. A circuit described in Balsa is compiled into a communicating network composed from a small (~35) set of handshake components. Balsa can be thought as of an public extension to Tangram. In particular the support for separate compilation and the use of a flexible communication enclosed input choice mechanism are claimed as useful additions to the expressiveness of Tangram. New

handshake components (which are the constituent parts of handshake circuits) are proposed which are used to implement this choice mechanism as well as more generalized forms of the existing Tangram system components.

### 2.5.2 Micropipelines

Micropipelines, introduced by Ivan Sutherland, use standard synchronous datapath logic to build asynchronous pipelines [25]. A micropipeline has altering computation stages separated by storage elements and control circuitry. This approach uses transition signaling for control along with bundled data. Sutherland describes several designs for the storage elements, called "event-controlled registers", which respond symmetrically to rising and falling transitions on inputs.

Computation on data in a micropipeline is accomplished by adding logic computation blocks between register stages. Since these blocks will slow down the data moving through them, the accompanying transition is delayed as well by the explicit delay elements, which must have at least as much delay in them as the worst-case logic block delay. The major benefit of the micropipeline design style is that the registers or latches at the boundaries of pipeline stages filter out logic hazards within the combinational logic. Thus, standard synchronous combinational logic design styles and supporting CAD tools can be used.

Although micropipelines is a powerful design style, which elegantly implements elastic pipelines, there are some problems with them as well. It delivers worst-case performance by adding delay elements to the control path to match worst-case computation times. Also there are delay assumptions that must be carefully verified. Finally, there is little guidance currently on how to use micropipelines for more complex (add speculative completion pros and cons) systems.

#### 2.5.3 Ad Hoc Design

Our final design methodology is ad hoc design. Although it may not seem like a design methodology, the ad hoc design approach implemented buy a skilful designer can lead to very competitive results. A design can be completely implemented in an ad hoc fashion, or can be initially developed using one of the methods above and then be optimized in an ad hoc sense.

An asynchronous design can be implemented the same way a synchronous design would, using synchronous components for the datapath. A matched delay can be used to indicate the completion of the computation. The control circuit can be implemented by modifying a synchronous FSM to work with input transitions rather than a global clock.

Another approach is the use self-resetting logic. Although self-resetting logic has a number of difficult to satisfy timing assumptions careful ad hoc design can achieve high throughput with self-resetting asynchronous circuits. The synchronous parts of the circuit can be replaced with self-resetting logic. Important aspects of self-resetting design such as data insertion and pulse generation would require an ad hoc approach. Or alternatively, an asynchronous circuit can be implemented using any of the approaches presented above and can be later optimized for speed, area or power using verifiable ad hoc optimizations.

# 2.6 Linear and Non-Linear Asynchronous Pipelines

This section presents the basics of linear and non-linear fine-grain asynchronous pipelines where each pipeline stage is derived through one of several basic templates.

#### 2.6.1 Linear Pipelines

A pipeline is a linear sequence of functional stages where the output of one stage is connected to the input of the next stage. Data signals, which flow from the inputs to the outputs of the pipeline, are also called as data tokens. A linear pipeline has no forking or joining stages. The tokens in the pipelines remain in a first in first out order (FIFO). In synchronous design the sequential functional stages are registers. These registers hold the data tokens and are controlled by a global clock signal. Depending on the implementation, on rising or falling edge of the clock, all the registers sample new data values which wait at their inputs. Since all the registers "see" the clock signal at the same time, the movement of one data token to the next register is synchronized to all other data tokens, and they all move at the same time. However there is no central global clock in asynchronous design therefore a data token in one stage only moves to the next stage if it is empty. The handshaking protocol between the two stages (the sender and the receiver) determines how the two stages inform each other when there is an empty space, when the data has been sent, if the data has been received by the next stage (receiver) and when the previous data holding stage (sender) can reset its data. The handshaking protocol is accomplished through a communication channel between the sender and the receiver. Although in this section we explain a communication channel under the context of pipelines, a communication channel can exist between any two asynchronous units. An asynchronous communication channel shown in Figure 3.1 is a bundle of wires and a protocol to communicate data between a sender and a receiver. For single rail encoding one wire per bit is used to transmit the data and an associated request line is sent to identify when data is valid. The associated channel is called a bundled-data channel. Alternatively for dual rail encoding the data is sent using two wires for each bit of information. Extensions to 1-of-N encoding also exist.

Both single-rail and dual-rail encoding schemes are commonly used, and there are tradeoffs between each. Dual-rail and 1-of-N encoding allow for data validity to be indicated by the data itself and are often used in QDI designs. Single-rail, in contrast, requires the associated request line, driven by a matched delay line, to always be longer than the computation, as we described in section 2.1.

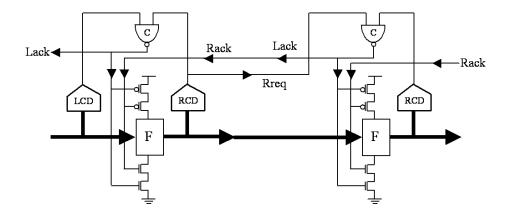

Figure 2-2: Pipeline channels

Figure 2-3: Synchronous vs. asynchronous pipelines

Figure 2-3 illustrates the difference between typical synchronous and asynchronous linear pipelines

Abstractly the operation of a general asynchronous pipeline with four-phase handshaking can be described as follows. Initially the pipeline is empty, and all the data lines as well as the handshaking signals *req* (the request signal) and *ack* (the acknowledgment signal) are de-asserted. The request signal req can be used if the data lines are single rail, to inform the next stage the arrival of data. On the other hand if the data lines are implemented with dual rail, conventionally, there is no need for the req signal. When the

first stage evaluates and generates an output the req signal is also assert. When the second stage evaluates it asserts its req signal as well as the ack signal to acknowledge the first stage that it has consumed the data. The first stage responds to this acknowledge signal by resetting its outputs. The first stage can only generate new data when the acknowledge signal is de-asserted, indicating that the second stage is ready to consume the second data token. When the third stage evaluates it will generate an ack signal to the second stage, which will cause it to reset its outputs as well as lower its ack and req signal. Since the second stage has lowered its ack signal it can now consume a second data token.

### 2.6.2 Fine Grain Pipelining

The design methodology in this thesis is targets fine grain pipelining and small cells, where the forward latency is two gate delays. Fine grain pipelining is achieved by dividing the processing blocks to even smaller cells where each cell has its own input and output completion detector. For example a 32 bit multiplier can be implemented by using a 32 bit input completion detector at the inputs and a 32 bit output completion detector at the outputs. When the multiplier completes it processing and generates a 32 bit output, the output completion detector detects it and combined with the input completion detector generates and acknowledge. However the multiplier can only accept a new input only when the whole multiplier has finished processing. Therefore the throughput is limited to how fast the multiplier can multiply two numbers, generate and acknowledge and then reset. As in the synchronous case the throughput of the multiplier can be increased by further pipelining the multiplier. In asynchronous design, this can be done by constructing the multiplier using small number of cells such as adders and other logic gates which have their own input and output completion detectors. Not only now can the multiplier accept new

input as soon as the first row of logic in the multiplier has evaluated and reset but also simplifies the 32 bit completion detectors into 1 bit input and output completion detectors. For a 2 dimensional structure such as a multiplier this is called *2D Fine Grain Pipelining*. Also since fine grain pipelining uses pre-designed templates it has an added benefit of cell reuse and faster design time.

## 2.6.3 Performance Analysis of Linear Pipelines

Determining the performance of an asynchronous pipeline can be more complex than determining the performance of a synchronous pipeline. In an asynchronous pipeline, control signals govern token flow with local handshaking. Each four phase token is composed of a data element and a reset spacer. At any instant, the pipeline stages not occupied by data elements or reset spacers can be described as containing a *hole* or *bubble*. Control logic only allows an element to flow forward when the stage it will occupy is empty. When an element does flow forward, it leaves behind an empty slot. Thus, bubbles flow backward as they displace forward-flowing data elements and reset spacers. The performance can be limited by the supply of tokens, the supply of bubbles or the local control handshaking between two pipeline stages. In a pipeline, the left or input environment supplies data tokens and the right or output environment supplies bubbles.

In an asynchronous pipeline the time it takes for a data token to flow from the inputs to the outputs of one pipeline stage is defined as *forward latency*. The *reverse or backward latency* specifies the delay from the acknowledgment of a stage's output to the acknowledgment of the predecessor's output. The time difference two tokens passing through the same pipeline stage is called *cycle time*. The cycle time is the total of the forward and backward latency.

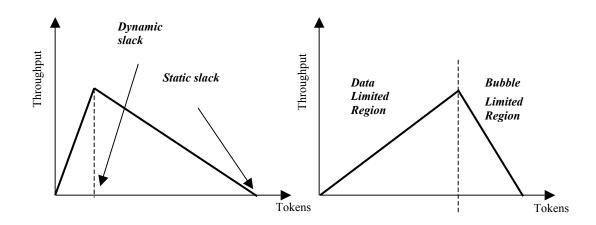

In an asynchronous pipeline, the per-stage forward or backward latency depends on the implementation of the circuit and the handshaking protocol. Pipeline stages, which can hold one data token using only one stage, are called *full buffers* (also known as *high capacity* or *slack*). Pipeline stages, which need two stages two hold one data token are called *half buffers*. Assuming that the right environment is not operating, or has stalled handshaking with the last stage of an asynchronous pipeline, and the left environment keeps inserting as much data tokens as it can, the maximum possible tokens that the pipeline can hold is defined as the *static slack* of the pipeline. Assuming that the left environment is asserting and the right environment is consuming data tokens as fast as the pipeline can operate, the number of tokens needed for the pipeline to operate at the highest throughput is called the *dynamic slack* of the pipeline.

For a pipeline where the forward latency is less than the backward latency, the cycle time is dominated by the backward latency. For the opposite case the cycle time will be dominated by the forward latency. The following figure illustrates the throughput vs. number of tokens for a linear asynchronous pipeline. The left side of the triangle shows the characteristic of an asynchronous pipeline operating in a data-limited region. In this region, as the data tokens are inserted more frequently the pipeline operates at a higher throughput. The speed of the pipeline is limited by how fast data can be inserted into the pipeline. The right side of the triangle shows the characteristic of an asynchronous pipeline operating in a bubble-limited region. In this region the right environment cannot consume the data provided by the asynchronous pipeline and therefore the data tokens start to accumulate in the pipeline. Another way to view this region is to say that the handshaking between pipeline stages is limiting the throughput at which tokens can be

processed and therefore the overall pipeline performance starts to degrade. The figure has two throughput vs. tokens triangles. The left one is for a forward-latency limited pipeline and the right one is for a backward-latency limited pipeline.

Figure 2-4: Throughput vs. tokens graphs

In order to determine the latencies and cycle time of a pipeline built out of a particular configuration of components in each stage, it is necessary to analyze the dependencies of the required sequences of transitions. These dependencies can be drawn in a marked graph [53], in which the nodes of the graph correspond to specific rising and falling transitions of circuit components, and the edges depict the dependencies of each transition on the output of other components. Unfolded dependency graphs are functionally equivalent to Signal Transition Graphs. STG's can be used to determine both the forward latency and the cycle time. The local cycle time is determined by *cyclic* paths in the STG. These cycles occur because a pipeline processes successive data tokens and the components in each stage go through a series of transitions. The transitions eventually

return a stage to the same *state*, where the state is defined by the output values of each component. Each transition in a STG can fire only when all of its predecessors have executed their specified transitions, and cannot fire again until all of its predecessors have fired again.

## 2.6.4 Non-Linear Pipelines

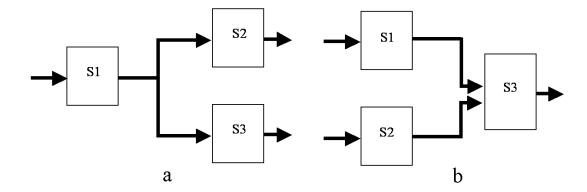

Recently many new asynchronous pipelines have been introduced. However most of them have been targeted for linear pipeline applications such as FIFOs. Real designs, however, require more complicated non-linear pipeline structures. In particular, linear pipeline stages have only a single input and a single output channel, where as non-linear pipelines stages can have multiple input and output channels. This section presents an overview of the challenges involved in designing non-linear pipelines. In particular we address issues with (i) synchronization with multiple destinations (for *forks*), and (ii) synchronization with multiple sources (for *joins*).

To introduce these issues we focus on *forks* and *joins*. A join is a pipeline stage with multiple input channels whose data is merged into a single output channel. A fork is a pipeline stage with one input channel and multiple output channels. Complex forks and joins can involve conditionally reading from or writing to channels based on the value of a control channel that is unconditionally read, as in a merge or split channel. Abstract illustrations of these channels are shown in Figure 3.4.

Figure 2-5: a) a fork and b) a join

Since a fork has multiple output channels, it must receive an acknowledgment signal from all of them before it precharges. A join, on the other hand, receives inputs from multiple channels and must broadcast its acknowledgment signal to all its input stages.

A join acts as a synchronization point for data tokens. The acknowledgment from the join should only be generated when all the input data has arrived. Otherwise a stage feeding a join, referred to as A, that is particularly slow in generating its data token may receive an acknowledgment signal when it should not, violating the 4-phase protocol. If the acknowledgment signal is de-asserted before the slow stage A generates its token, the token is not consumed by the join, as it should be. In fact, this token may cause the join to generate an extra token at its output, thereby corrupting the intended synchronization.

A conditional split is a combined fork and join where a control channel is used to determine which output is generated. The control may indicate to send the input data to any of the output channels, any combination of the output channels, or none of them. The third option is also known as a *skip*.

A conditional join is a join where the control signal, select, comes from another pipeline stage. The select signal controls which incoming channel should be read.

Figure 2-6: Fundamental non-linear pipeline structures

# Chapter 3

# 3. New High Speed QDI Asynchronous Pipelines

In this chapter we introduce two new QDI templates that provide significant performance improvements over those proposed by Caltech without sacrificing quasi delay insensitivity. The key idea is to reduce the complexity of internal circuitry by intelligently reducing concurrency and using an additional wire for communication between pipeline stages. We present two templates: one that is a half-buffer which requires two pipeline stages to hold one data token and one full-buffer template that can itself hold one data token.

We first give background on Caltech's commonly used QDI templates, the Weak-Conditioned Half Buffer (*WCHB*), the Precharged Half Buffer (*PCHB*), and the Precharged Full Buffer (*PCFB*) templates [24].

## 3.1 Caltech's QDI templates

#### 3.1.1 WCHB

Figure 3-1 shows a WCHB template for a linear pipeline with a left (L) and right (R) channel and an optimized WCHB dual-rail buffer. L0 and L1, R0 and R1 identify the false and true dual rail inputs and outputs, respectively. *Lack* and *Rack* are active-low acknowledgment signals. Note that we do not show staticizers that are required to hold state at the output of all C-elements.

The operation of the buffer is as follows. After the buffer has been reset, all data lines are low and acknowledgment lines, *Lack* and *Rack*, are high. When data arrives by one of the input rails going high, the corresponding C-element output will go low, lowering the left-side acknowledgment *Lack*. After the data is propagated to the outputs through one of the inverters, the right environment will assert *Rack* low, acknowledging that the data has been received. Once the input data resets, the template raises *Lack* and resets the output.

Since the L and R channels cannot simultaneously hold two distinct data tokens, this circuit is said to be a *half buffer* or has *slack* ½ [24]. This WCHB buffer has a cycle time of 10 transitions, which is significantly faster than buffers based on other QDI pipeline templates.

Another feature of the WCHB template is that the validity and neutrality of the output data R implies the validity and neutrality of the corresponding input data L. This is called weak-conditioned logic [20] and we will discuss its advantages and disadvantages after we discuss non-linear pipeline templates.

Figure 3-1: WCHB

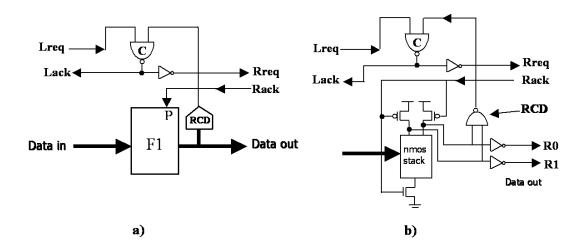

## 3.1.2 PCHB and PCFB

Figure 3-2 shows the template for a pre-charged half-buffer (PCHB). Unlike the WCHB, the test for validity and neutrality is checked using an input completion detector. The input completion detector is denoted as LCD and the output completion detector as RCD.

Figure 3-2: a) PCHB and b) PCFB templates

Figure 3-3: a) PCHB and b) PCFB STG

The function block need not be weak-conditioned logic and thus can evaluate before all the inputs have arrived (if the logic allows). However, the template only generates an acknowledgment signal *Lack* after all the inputs have arrived *and* the output has evaluated. In particular, the LCD and the RCD are combined using a C-element to generate the acknowledgment signal.

A few minor aspects of this template should also be pointed out. First, because the C-element is inverting the acknowledgment signal is an active-low signal. Second, the *Lack* signal is often buffered using two inverters before being sent out. Another two inverters are also often added to buffer the internal signal *en* that controls the function block. For simplicity, these buffering inverters will not be shown in the figures in this paper.

The protocol for a PCHB pipeline stage is captured by the STG for a three-stage pipeline illustrated in Figure 3-3. From the STG, it is possible to derive the pipeline's analytical cycle time:

$$T_{PCHB} = 3. t_{Eval} + 2. t_{CD} + 2. t_c + t_{prech}$$

Due to the extra buffering and bubble shuffling, the cycle time generally amounts to 14 gate delays or *transitions*.

The PCFB template and its STG are shown in Figure 3-2(b) and Figure 3-3(b). The PCFB is more concurrent than the PCHB because its L and R handshakes reset in parallel at the cost of requiring an additional state variable. The PCFB analytical cycle time is:

$$T_{PCFB} = 2. t_{Eval} + 2. t_{CD} + 2. t_c + t_{prech}$$

which generally amounts to 12 transitions. Here  $t_{CD}$  takes two transitions, one of the C-elements takes one transition, and the other takes two transitions.

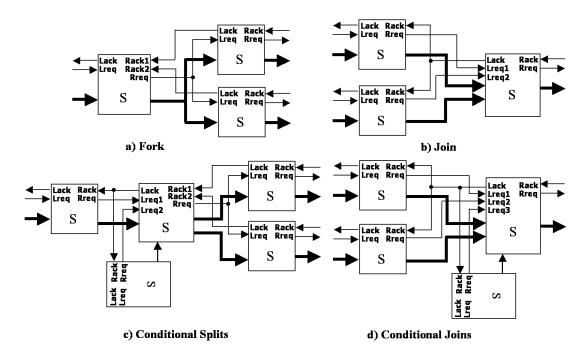

### 3.1.3 Why Input Completion Sensing?

A join is a pipeline stage with multiple input channels whose data is merged into a single output channel. A fork is a pipeline stage with one input channel and multiple output channels. Complex forks and joins can involve conditionally reading from or writing to channels based on the value of a control channel that is unconditionally read, as in a merge or split channel.

Since a fork has multiple output channels, it must receive an acknowledgment signal from all of them before it precharges. A join, on the other hand, receives inputs from multiple channels and must broadcast its acknowledgment signal to all its input stages.

A join acts as a synchronization point for data tokens. The acknowledgment from the join should only be generated when all the input data has arrived. Otherwise a stage feeding a join, referred to as A, that is particularly slow in generating its data token may receive an acknowledgment signal when it should not, violating the 4-phase protocol. If the acknowledgment signal is deasserted before the slow stage A generates its token, the token is not consumed by the join, as it should be. In fact, this token may cause the join to generate an extra token at its output, thereby corrupting the intended synchronization.

Validity of data should be checked on all input channels before the acknowledgment signal is asserted to prevent the incorrect insertion of a token caused by a slow/late input channel. Neutrality should be checked to guarantee that the previous stages have been precharged, so that the acknowledgment signal is not deasserted too early, thereby violating the four-phase protocol on any stage slow to precharge.

The templates presented in this section check validity and neutrality in different ways. Because the function block in WCHB template is weak-conditioned, the output completion detector implicitly checks validity and neutrality of the input data token. In the WCHB buffer the weak conditioned function block is a simple C-element. However, for more complex non-linear pipelines, weak-conditioned function blocks unfortunately require complex nmos and pmos networks. This results in slower forward latency and bigger transistor sizes. As an example, a weak-conditioned dual-rail OR is shown in Figure 3-4.

Figure 3-4: An OR gate implementation using weak conditioned logic

## 3.2 New QDI Templates

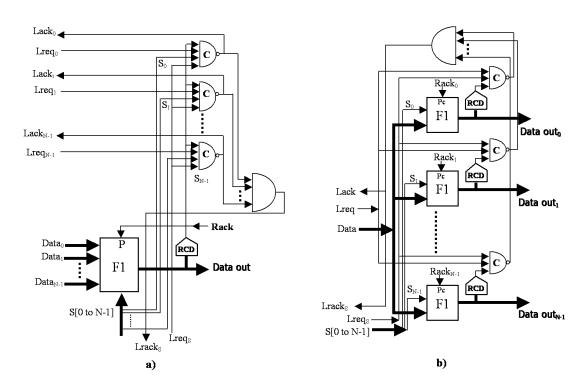

One optimization that can be applied to the PCHB and PCFB templates is to merge the LCD of one stage with the RCD of the other by adding an additional request line to the channel. This is shown in Figure 3-5 for a PCHB template.

Figure 3-5: Optimized PCHB for a 1-of-N+1 channel

The request line indicates the assertion/de-assertion of the input data, as in the bundled-data channel. However in contrast to a bundled-data channel, the data is sent using 1-of-N encoding, yielding what we call a 1-of-N+1 channel. The request line, at least from the channel point of view, may appear redundant. However, the request line enables the removal of the input completion detector thereby saving area and reducing capacitance on the data lines. Moreover, the request line does not significantly impact performance, the template is still QDI, and the communication between stages remains delay-insensitive.

In this section we propose two new 1-of-N+1 QDI templates that intelligently reduce concurrency to reduce the stack size of the function blocks and thereby improve performance.

#### **3.2.1 RSPCHB**

The key goal of the RSPCHB compared to the PCHB is to eliminate the need of the enable signal *en* from the control of the function block. We now explain that the need for this enable signal is only to support concurrency in the system that effectively does not improve performance.

More specifically, in the PCHB template the output of the LCD and RCD are combined using a C-element to generate the acknowledgment signal *Lack*. This supports the integration of the handshaking protocol with the validity and neutrality of both input and output data, which removes the need for the function block to be weak-conditioned, but also requires the use of the *en* signal. It is this replacement however that introduces more concurrency than is necessary.

In particular, in the case of a join, the non-weak-conditioned function block may generate an output as soon as one the input channels provide data. In response, the RCD of the join will assert its output. Meanwhile, any subsequent stage can receive this data, evaluate, assert both its LCD and RCD outputs, and assert its acknowledgment signal. Although the join can receive this acknowledgment, it will not precharge until after *en* is asserted. The *en* signal delays the precharge of the circuit until after the acknowledgement to the input stages has been asserted. This delay is critical to prevent the precharge from triggering the RCD to deassert which would prevent the C-element from ever generating the acknowledgment.

If only the generation of the acknowledgment signal from any stage subsequent to the join was delayed until all input data to the join has arrived and been acknowledged, then the *en* signal could be safely removed. In fact, such a delay of the acknowledgement would not generally impact performance because the join is the performance bottleneck for the subsequent stages. Therefore, this added concurrency is essentially unnecessary.

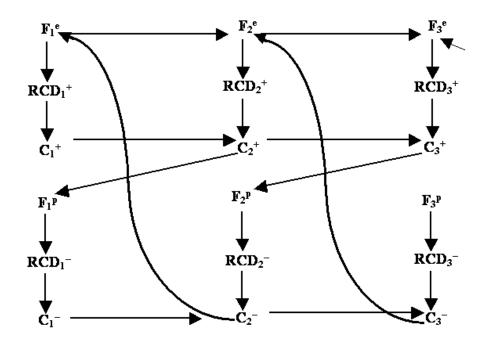

We propose a different pipeline template, which reduces this unnecessary concurrency to eliminate the internal *en* signal, thereby reducing the transistor stack sizes in the function block. We refer to this new QDI pipeline template, illustrated in Figure 3.6(a), as a *Reduced*

Stack Precharged Half Buffer (RSPCHB). A specific form of this template for dual-rail data is shown in Figure 3-6(b). Notice that we optimized the RCD block by tapping its inputs before the output inverter and using a NAND gate instead of an OR gate.

The unique feature of the RSPCHB is that it derives the request line from the output of the C-element instead of the RCD. (In particular, since the output of the C-element is active low and the request line is active high, the output of the C-element is sent through an inverter before driving *Rreq*.) The impact of this change is that the assertion/de-assertion of *Rreq* is delayed until after all *Lreq*'s are asserted/de-asserted.

Figure 3-6: a) Abstract and b) detailed QDI RSPCHB pipeline template

Figure 3-7: The STG of the RSPCHB

As a consequence, the acknowledgment from a subsequent stage of the join may be delayed until well after its data inputs and outputs are valid. More specifically, the stage will delay the assertion of its acknowledgment signal until all *Lreq*'s are asserted which can occur arbitrarily later than the associated data lines becoming valid. This extra delay, however, has no impact on steady-state system performance because the join stage is the bottleneck, waiting for all its inputs to arrive before generating its acknowledgement. In fact, this change yields a template with no less concurrency than WCHB.

The advantage of this generation of the request line is that the function block does not need to be guarded by the enable signal. In particular, it is now sufficient to guard the function block solely by the Pc signal because the Pc signal now properly identifies when inputs and outputs are valid. Namely, the function block is allowed to evaluate when Pc is deasserted which occurs only after all inputs and outputs data lines are reset. Similarly, it is

allowed to precharge when  $P\epsilon$  is asserted which occurs only after all input and output data lines are valid.